# Chapter 1: The digital abstraction Computer Structure - Spring 2007

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary questions**

- Can you justify or explain the saying that "computers use only zeros and ones"?

- Can you explain the following anomaly? The design of an adder is a simple task. However, the design and analysis of a single electronic device (e.g., a single gate) is a complex task.

# **Digital Circuits vs. Analog Devices**

| Property    | Digital Circuit           | Analog Device                       |

|-------------|---------------------------|-------------------------------------|

| values      | {0,1}                     | $\mathbb{R}$                        |

| description | simple (Boolean function) | complicated (dif-<br>ferential eq.) |

| real?       | abstract model            | very real                           |

**Conclusion:** much easier to use the digital abstraction than the realistic, complete, complicated analog model.

# **More questions**

what is an analog device? (components, behavior)

- in what way does a digital circuit model an analog device?

- can every analog device be modeled as a digital circuit?

- what type of digital circuits do we want?

- why is one inverter better than another?

- how can we tell if an analog device is a gate (say, an inverter)?

## **Transistors**

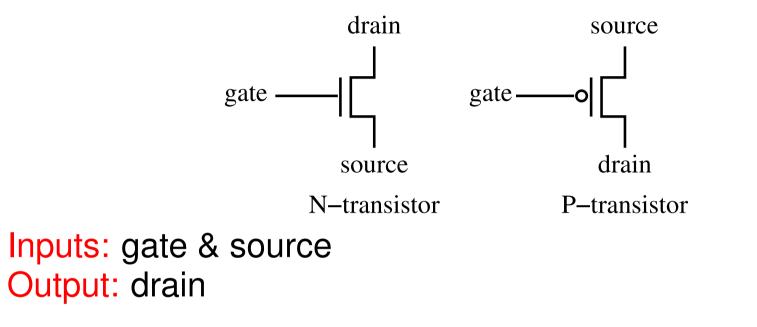

Computers  $\leftarrow$  VLSI chips  $\leftarrow$  gates & flip-flops  $\leftarrow$  transistors Transistors are the basic components. Most common VLSI technology is called CMOS. In CMOS: only two types of transistors:

N-transistor

P-transistor

in case you are curious:

VLSI = Very Large Scale Integration (which means "millions of transistors placed on one small chip") CMOS = Complementary Metal Oxide Semiconductor (which means that both NMOS and PMOS transistors are used).

## **N-transistor & P-transistor**

(not accurate! just for the sake of this discussion)

#### **N-transistor & P-transistor**

Functionality of N-transistor:

- If v(gate) = high, then resistance(source, drain) = 0 (and then  $v(drain) \leftarrow v(source)$ )

- If v(gate) = low, then  $resistance(source, drain) = \infty$

Functionality of P-transistor:

If v(gate) = high, then  $resistance(source, drain) = \infty$

• If v(gate) = low, then resistance(source, drain) = 0

Story true if: v(s) = high in P & v(s) = low in N.

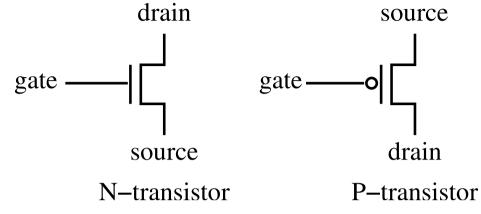

# **Example: a CMOS inverter**

IN = low:

P-transistor is conducting

N-transistor is not conducting

v(OUT) = high

IN = high:

- P-transistor is not conducting

- N-transistor is conducting

$\Rightarrow v(OUT) = low$

#### **Qualitative Analysis vs. Quantitative Analysis**

Qualitative analysis:

- gives an idea about "how an inverter works".

- no idea about actual voltages of output as a function input voltage.

- no idea about how long it takes the output to stabilize.

Quantitative analysis:

- based on precise modeling of transistor.

- computes precise input-output relationship.

- requires a lot of work (usually done with the aid of a computer program called SPICE).

# **Analog signals**

An analog signal is a real function

$f: \mathbb{R} \to \mathbb{R},$

where f(t) = voltage as a function of the time.

Assumption: wires have zero resistance, zero capacity, and signals propagate through wires without delay.  $\Rightarrow$  voltage along a wire is identical at all times.

Since a signal describes the voltage (i.e. derivative of energy as a function of charge), we also assume that a signal is a continuous function.

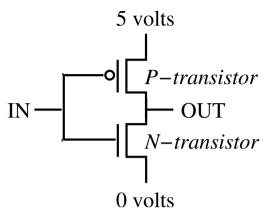

# **Digital signals**

A digital signal is a function

```

g: \mathbb{R} \to \{0, 1, \text{non-logical}\}.

```

The value of a digital signal describes the logical value carried along a wire as a function of time.

- zero & one : logical values.

- non-logical: indicates that the signal is neither zero or one.

#### **Interpreting analog signals as digital signals**

Q: How does one interpret an analog signal as a digital signal?

naive answer: define a threshold voltage V'. Consider an analog signal f(t).

The digital signal dig(f(t)) is defined as follows.

$$\operatorname{dig}(f(t)) \stackrel{\scriptscriptstyle \triangle}{=} \begin{cases} 0 & \text{if } f(t) < V' \\ 1 & \text{if } f(t) > V' \end{cases}$$

Q: is this a useful definition?

# problems with definition of dig(f(t))

- All devices in a circuit must use exactly the same threshold V'. This is impossible due to manufacturing tolerances.

- Perturbations of f(t) around the threshold V' lead to unexpected values of dig(f(t)).

Example: Measure weight w by measuring the length l of a spring. Suppose we wish to know if w > w'. This can be done by checking if l > l'. However, spring length oscillates around l. If l ≈ l', then comparison requires a long time.

- $\Rightarrow$  must use separate thresholds for 0 and for 1.

#### **Interpreting analog signals as digital signals**

Q: How does one interpret an analog signal as a digital signal?

A: Two voltage thresholds are defined:  $V_{low} < V_{high}$ . Consider an analog signal f(t).

The digital signal dig(f(t)) is defined as follows.

$$\textit{dig}(f(t)) \triangleq \begin{cases} 0 & \text{if } f(t) < V_{\textit{low}} \\ 1 & \text{if } f(t) > V_{\textit{high}} \\ \text{non-logical} & \text{otherwise.} \end{cases}$$

#### digital interpretation of an analog signal

#### did we solve the problems of a single threshold?

■ manufacturing requirements: a low output must be  $\leq V_{low}$  & a high output must be  $\geq V_{high}$ .

fluctuations of f(t) around V<sub>low</sub> still cause fluctuations of dig(f(t)).

However, these fluctuations are between 0 and "non-logical" (not between 0 and 1). This is still a problem, but not as bad...

Will noise cause a problem?

Noise = undesired changes to f(t). Back to the example of a weight hanging from a spring: wind causes changes in the spring length and disturbs measurement of spring length.

#### **An inverter**

Q: define an inverter.

**A**:

$dig(OUT(t)) \triangleq \begin{cases} 0 & \text{if } dig(IN(t)) = 1\\ 1 & \text{if } dig(IN(t)) = 0\\ \text{arbitrary } \text{otherwise.} \end{cases}$

We will see shortly that: noise  $\Rightarrow$  cannot use these definitions to build correct circuits.

Before we discuss these issues, we must introduce transfer functions and noise...

## **Transfer functions**

**DEF:** transfer function - the relation between the voltage at an output of a gate and the voltages of the inputs of the gate.

**Example:** An inverter with an input x and an output y. The value of the signal y(t') at time t' is a function of the signal x(t) in the interval  $(-\infty, t']$ .

Static transfer function: if the input x(t) is stable for a sufficiently long period of time and equals  $x_0$ , then the output y(t) stabilizes on a value  $y_0$  that is a function of  $x_0$ .

history vs. present: if a device does not have a static transfer function, then the device is a memory device not a logical gate.

## **Static transfer function**

Let *G* denote a gate with one input *x* and one output *y*. **DEF**: A function  $f : \mathbb{R} \to \mathbb{R}$  is a static transfer function of a gate *G* if

$$\exists \Delta > 0 \ \forall x_0 \ \forall t_0 :$$

$$\forall t \in [t_0 - \Delta, t_0] \ x(t) = x_0 \implies y(t_0) = f(x_0).$$

- $\blacksquare$   $\Delta$  propagation delay (time required for stable output)

- $\blacksquare x_0$  stable input voltage

- $\bullet$  to time in which y(t) is measured

## **Static transfer function - remarks**

(1) Since circuits operate over a bounded range of voltages, static transfer functions are usually only defined over bounded domains and ranges (say [0, 5] volts).

#### **Static transfer function - remarks**

(2) Allow perturbations of x(t) and y(t).

$$\begin{aligned} \forall \epsilon \ \exists \delta, \Delta > 0 \ \forall x_0, t_1, t_2 : \\ \forall t \in [t_1, t_2] : |x(t) - x_0| \leq \delta \\ & \Longrightarrow \\ \forall t \in [t_1 + \Delta, t_2] : |y(t) - f(x_0)| \leq \epsilon \end{aligned}$$

- $\delta$  measures stability of input x(t)

- $\bullet$  measures stability of output y(t)

- $[t_1, t_2]$  interval during which x(t) is  $\delta$ -stable.

- $[t_1 + \Delta, t_2]$  interval during which y(t) is  $\epsilon$ -stable.

**Propagation delay**  $\Delta$  depends only on  $\epsilon$  (which is fixed and the same for all voltages).

## back to the definition of an inverter

$$dig(OUT(t)) \triangleq \begin{cases} 0 & \text{if } dig(IN(t)) = 1 \\ 1 & \text{if } dig(IN(t)) = 0 \\ \text{arbitrary otherwise.} \end{cases}$$

or equivalently,

$$IN(t) < V_{low} \Longrightarrow OUT(t) > V_{high}$$

$IN(t) > V_{high} \Longrightarrow OUT(t) < V_{low}$

Q: Define a NAND-gate.

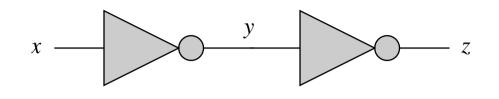

# $\begin{array}{c} \text{Noise} \\ wire \\ \end{array} \rightarrow B(t) \end{array}$

Noise signal: the difference B(t) - A(t). (reference signal = A(t)). Q: what causes noise?

A: The main source of noise is heat. Heat causes random movement of electrons. These random movements do not cancel out perfectly, and random currents are created. These random currents create perturbations in the voltage.

## **Bounded noise model**

- Bounded noise model the noise signal along every wire has a bounded absolute value.

- Uniform bounded noise model:

```

\exists \epsilon > 0 such that : | noise | \leq \epsilon.

```

Justification - noise is a random variable whose distribution has a rapidly diminishing tail. If the e is sufficiently large, then

$Prob[|noise| > \epsilon] \approx 0.$

#### The digital abstraction in the presence of noise

Assume that:

•

$$x > V_{high}$$

, so  $dig(x) = 1$ ,

•  $y = V_{low} - \epsilon'$ , for a very small  $\epsilon' > 0$

•  $\Rightarrow dig(z) = 1$ .

What if input to 2nd inverter equals  $y(t) + n_y(t)$ ?

If  $n_y(t) > \epsilon'$ , then  $dig(y(t) + n_y(t)) =$  non-logical, and can't deduce that dig(z) = 1.

$\Rightarrow$  must strengthen the digital abstraction!

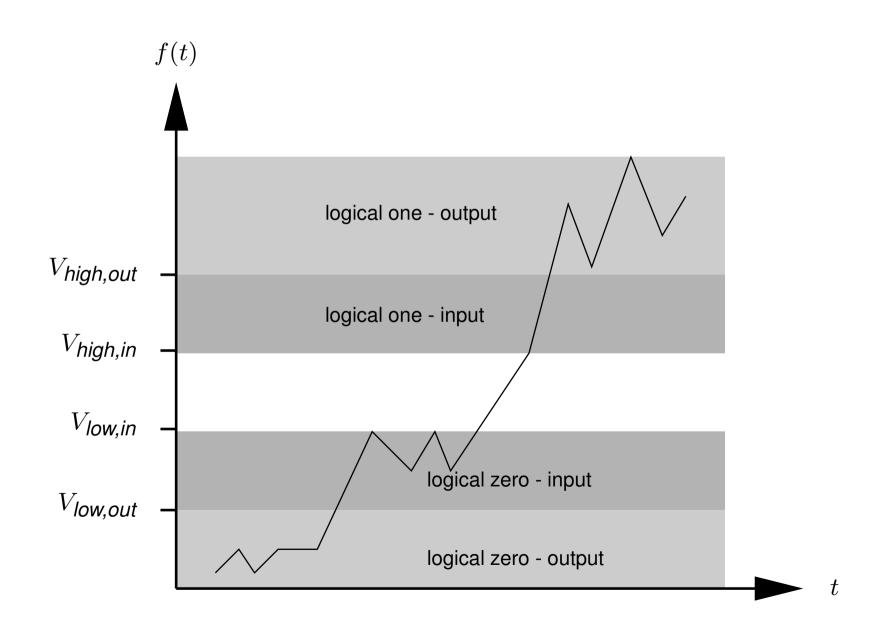

**Redefining the digital interpretation of analog signals**

Deal with noise: interpret input signals and output signals differently.

Input Signal: a signal measured at an input of a gate.

**Output Signal:** a signal measured at an output of a gate.

#### **Redefining the digital interpretation (cont.)**

Instead of two thresholds,  $V_{low}$  and  $V_{high}$ , we define the following four thresholds:

- *V*<sub>low,in</sub> an upper bound on a voltage of an input signal interpreted as a logical zero.

- *V*<sub>low,out</sub> an upper bound on a voltage of an output signal interpreted as a logical zero.

- Vhigh, in a lower bound on a voltage of an input signal interpreted as a logical one.

- Vhigh,out a lower bound on a voltage of an output signal interpreted as a logical one.

These four thresholds satisfy the following equation:

$$V$$

low,out <  $V$ low,in <  $V$ high,in <  $V$ high,out ·

#### **Redefining the digital interpretation (cont.)**

#### **Digital interpretation of input & output signals**

Consider an input signal  $f_{in}(t)$ . The digital signal  $dig(f_{in}(t))$  is defined as follows.

$$dig(f_{in}(t)) \triangleq \begin{cases} 0 & \text{if } f_{in}(t) < V \text{low,in} \\ 1 & \text{if } f_{in}(t) > V \text{high,in} \\ \text{non-logical} & \text{otherwise.} \end{cases}$$

Consider an output signal  $f_{out}(t)$ . The digital signal  $dig(f_{out}(t))$  is defined analogously.

$$dig(f_{out}(t)) \triangleq \begin{cases} 0 & \text{if } f_{out}(t) < V \text{low,out} \\ 1 & \text{if } f_{out}(t) > V \text{high,out} \\ \text{non-logical} & \text{otherwise.} \end{cases}$$

## **Noise margins**

The differences

$$V$$

low,in <sup>- V</sup>low,out and Vhigh,out <sup>- V</sup>high,in

are called noise margins.

Claim: Suppose that a wire transmits an output signal  $f_{out}(t)$  to an input signal  $f_{in}(t)$ . Suppose that |n(t)| is less than the noise margin. If  $dig(f_{out})(t) \in \{0,1\}$ , then  $dig(f_{in}(t)) = dig(f_{out}(t))$ .

**Proof:** If the absolute value of the noise n(t) is bounded by the noise margins, then an output signal  $f_{out}(t) < V_{low,out}$ will result with an input signal  $f_{in}(t) = f_{out}(t) + n(t) < V_{low,in}$ .

### **Inverter - revisited**

We are now ready to define an inverter.

**Definition:** Let *G* denote a device with one input *x* and one output *y*. The device *G* is an inverter if its static transfer function f(x) satisfies:

$$x(t) < V$$

low, in  $\implies y(t) > V$ high, out

$x(t) > V$ high, in  $\implies y(t) < V$ low, out.

Q: can you define a NAND-gate?

## Logical & stable analog signals

back to the zero-noise model (to simplify the discussion)...

- logical signal: f(t) is logical at time t if  $dig(f(t)) \in \{0, 1\}$ .

- stable signal: f(t) is stable during the interval  $[t_1, t_2]$  if f(t) is logical for every  $t \in [t_1, t_2]$ .

Claim: If an analog signal f(t) is stable during the interval  $[t_1, t_2]$  then one of the following holds:

- **1.** dig(f(t)) = 0, for every  $t \in [t_1, t_2]$ , or

- **2.** dig(f(t)) = 1, for every  $t \in [t_1, t_2]$ .

**Proof:** Continuity of  $f(t) \& V_{low} < V_{high}$

## Logical & stable digital signals

Let x(t) denote a digital signal. logical signal: x(t) is logical at time t if  $x(t) \in \{0, 1\}$ . stable signal: x(t) is stable during the interval  $[t_1, t_2]$  if x(t) is logical for every  $t \in [t_1, t_2]$ .

# **Summary**

- Signals analog & digital

- Noise bounded noise model & zero noise model

- Digital interpretation of analog signals

- Transfer functions

- Definition of gate (e.g. inverter) using transfer function

- Stable & logical signals

#### Chapter 2: Foundations of combinational circuits Computer Structure - Spring 2007

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary Questions**

- Does every collection of gates and wires constitute a combinational circuit?

- Which of these tasks is easy?

- Check if a circuit is combinational.

- Simulate a combinational circuit.

- Estimate the propagation delay of a combinational circuit.

- Suggest criteria for comparing functionally equivalent combinational circuits.

### Goals

- define combinational circuits.

- prove that every Boolean function can be implemented by a combinational circuit.

- prove that every combinational circuit implements a Boolean function.

- present an algorithm for simulating a combinational circuit.

- present an algorithm for analyzing the delay of a combinational circuit.

### **Boolean functions**

$\{0,1\}^n$  - the set of *n*-bit strings. A Boolean function - a function  $f: \{0,1\}^n \to \{0,1\}^k$ .

- *n*: input length

- k: output length

### **Gates & static transfer functions**

**DEF:** A gate is a device whose functionality is specified by a static transfer function.

$\begin{aligned} \exists \Delta > 0 \\ \forall x_0 \end{aligned}$  $\forall t \in [t_1, t_2] : x(t) = x_0 \implies \forall t \in [t_1 + \Delta, t_2] : y(t) = f(x_0). \end{aligned}$

This means that *output = func (input)* if the input did not change for a while.

This does not mean that the output must be logical (even if the input is fixed).

## **Extension of** dig(x) **to vectors**

- Suppose  $\vec{y} \in \mathbb{R}^n$ , where  $\vec{y} = (y_1, y_2, \cdots, y_n)$ .

- The function  $dig_n : \mathbb{R}^n \to \{0, 1, \text{non-logical}\}^n$  is defined by

$$dig_n(y_1, y_2, \cdots, y_n) \stackrel{\scriptscriptstyle riangle}{=} (dig(y_1), dig(y_2), \cdots, dig((y_n))).$$

To simplify notation, we denote dig<sub>n</sub> simply by dig when the length n of the vector is clear.

## **Def: combinational gate**

**DEF**: Consider a gate *G* with *n* inputs (denoted by  $\vec{x}$ ) and *k* outputs (denoted by  $\vec{y}$ ). The gate *G* is a combinational gate if there exists a  $\Delta > 0$ , such that, for all  $\vec{x}(t) \in \mathbb{R}^n$ ,

$$\forall t \in [t_1, t_2] : \operatorname{dig}(\vec{x}(t)) \in \{0, 1\}^n$$

$$\Rightarrow \quad \forall t \in [t_1 + \Delta, t_2] : \operatorname{dig}(\vec{y}(t)) \in \{0, 1\}^k.$$

Remark:

- Logically stable input  $\Rightarrow$  logical output.

- Static transfer function satisfies:

$$\operatorname{dig}(\vec{x}) \in \{0,1\}^n \Rightarrow \operatorname{dig}(f(\vec{x})) \in \{0,1\}^k.$$

$\vec{x}$  may fluctuate but must remain logically stable.

#### **Boolean functionality of a combinational gate**

Suppose  $f : \mathbb{R}^n \to \mathbb{R}^k$  is a static transfer function of a combinational gate G.

Define a Boolean function  $B_f : \{0,1\}^n \to \{0,1\}^k$  as follows. Given a Boolean vector  $(b_1, \dots, b_n) \in \{0,1\}^n$ ,

$$x_{i} \triangleq \begin{cases} V_{low} - \varepsilon & \text{if } b_{i} = 0\\ V_{high} + \varepsilon & \text{if } b_{i} = 1. \end{cases}$$

The Boolean function  $B_f$  is defined by

$$B_f(\vec{b}) \stackrel{\scriptscriptstyle riangle}{=} dig(f(\vec{x})).$$

*G* combinational circuit  $\Rightarrow$  *dig*( $f(\vec{x})$ ) is logical  $\Rightarrow$   $B_f$  is a Boolean function.

#### **Boolean functionality of a combinational gate - cont.** Since

$$B_f(\vec{b}) \stackrel{\scriptscriptstyle riangle}{=} dig(f(\vec{x})).$$

we can rephrase

$$dig(\vec{x}) \in \{0,1\}^n \Rightarrow dig(f(\vec{x})) \in \{0,1\}^k.$$

by

$$dig(\vec{x}) \in \{0,1\}^n \Rightarrow dig(f(\vec{x})) = B_f(dig(\vec{x})).$$

$\Rightarrow$  Claim: In a combinational gate, the relation between the logical values of the inputs and the logical values of the outputs is specified by a Boolean function.

## A consistent combinational gate

propagation delay - upper bound on the amount of time that elapses from the moment that the inputs (nearly) stop changing till the moment that the output (nearly) equals the value of the static transfer function.

**DEF:** A combinational gate *G* with inputs  $\vec{x}(t)$  and outputs  $\vec{y}(t)$  is consistent at time *t* if  $dig(\vec{x}(t)) \in \{0,1\}^n$  and  $\vec{y}(t) = B_f(dig(\vec{x}(t)))$ .

propagation delay - upper bound on time that elapses from logically stable inputs till gate is consistent.

## brief roundup

static transfer func  $\Rightarrow$  gate  $\Rightarrow$  comb. gate where

- gate: *o*utputs = func(inputs)

- combinational gate: *l*og. stable inputs  $\Rightarrow$  logical outputs

- consistency : when  $dig(\vec{y}) = B_f(dig(\vec{x}))$ .

- propagation delay: upper bound on time needed to reach consistency.

Very helpful if you need to deal with the following question: Is a device G a good candidate for an AND-gate?

Not helpful if you are given a library of gates to work with. In this case one prefers not to deal with analog signals...

## **Back to the digital world**

- digital signals refer to input and output signals as digital signals.

- goals for combinational gates:

- specification specify functionality using a Boolean function.

- consistency define when a gate satisfies the specification.

- performance quantify how fast it takes a gate to satisfy the specification.

- propagation delay loosen definition (allow analog inputs to change as long as they are logically stable)

## **Specification & Consistency**

- Consider a combinational gate G with 2 inputs, denoted by  $x_1, x_2$ , and a single output, denoted by y.

- $x_1(t), x_2(t)$  the digital signals corresponding to inputs.

- y(t) the digital signal corresponding to the output.

- $B: \{0,1\}^2 \rightarrow \{0,1\}$  a binary function (specification)

**DEF:** *G* is consistent with the Boolean function *B* at time *t* if the input values are digital at time *t* and

$y(t) = B(x_1(t), x_2(t)).$

### **Propagation delay of comb. gate**

**DEF:** A combinational gate *G* implements a Boolean function  $B : \{0, 1\}^2 \rightarrow \{0, 1\}$  with propagation delay  $t_{pd}$  if the following holds.

For every  $\sigma_1, \sigma_2 \in \{0, 1\}$ , if  $x_i(t) = \sigma_i$ , for i = 1, 2, during the interval  $[t_1, t_2]$ , then

$$\forall t \in [t_1 + t_{pd}, t_2] : y(t) = B(\sigma_1, \sigma_2).$$

Equivalently,

$$x_1, x_2$$

stable in  $[t_1, t_2]$

$\Rightarrow$

$G$  is consistent with  $B$  in the interval  $[t_1 + t_{pd}, t_2]$ .

### **Propagation delay - remarks**

- If  $t_2 < t_1 + t_{pd}$ , then the statement in the above definition is empty.

- Propagation delay is an upper bound. The actual amount of time that passes till a combinational gate is consistent is very hard to compute (there is also randomness involved). We may always be overly pessimistic (i.e., using a propagation delay that is larger than the actual delay will not introduce errors).

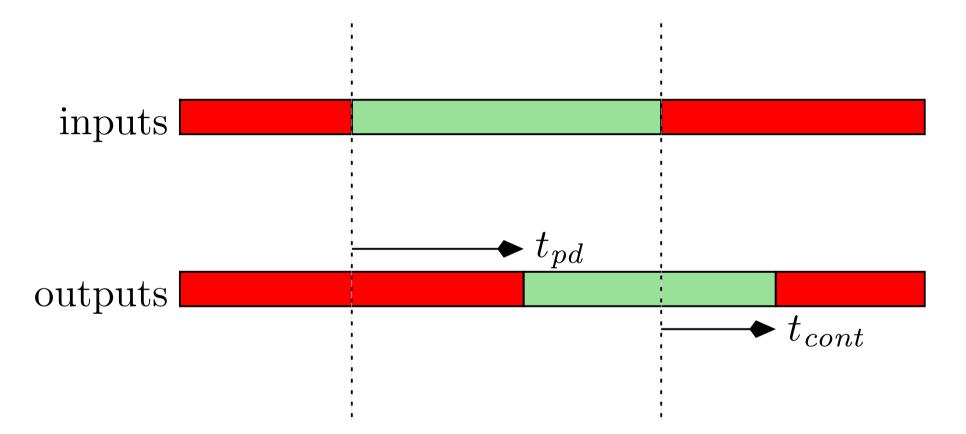

## **Contamination delay**

Contamination delay - a lower bound on the amount of time that the output of a consistent gate remains stable after its inputs stop being stable.

Contamination delay tells us how fast an output can "react" to a change in the input

We we will assume that the contamination delay is zero.

#### **Example: propagation delay and contamination delay**

#### *x*-axis: time.

- red segments: signal is not guaranteed to be logical.

- green segments: signal is guaranteed to be stable.

## **Combinational circuits - building blocks**

Combinational circuits are built of combinational gates and wires & nets.

## **Combinational gates**

- Implement a Boolean function.

- Since we consider only combinational gates, we refer to a combinational gate, in short, as a gate.

- Typical gates: inverter (NOT-gate), OR-gate, NOR-gate, AND-gate, NAND-gate, XOR-gate, NXOR-gate, multiplexer (MUX).

- fan-in : number of input terminals (typically, at most 3).

Input ports denoted by the set  $\{in(G)_i\}_{i=1}^n$ , where *n* denotes the fan-in of *G*.

Output ports denoted by the set  $\{out(G)_i\}_{i=1}^k$ , where k denotes the number of output ports of G.

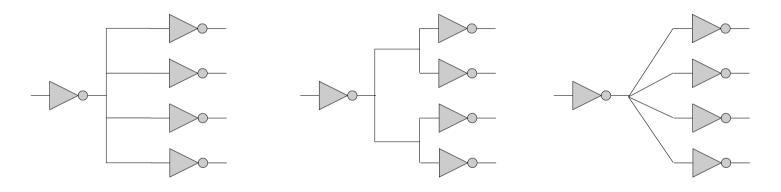

### Wires & Nets

Wires connect points to each other. Very often we need to connect several terminals (i.e. inputs and outputs of gates) together.

Ignore how connections are actually made.

Net - subset of terminals that are connected by wires. In the digital abstraction we assume that the signals all over a net are identical (why?).

fan-out of a net N - the number of input terminals that are connected to N.

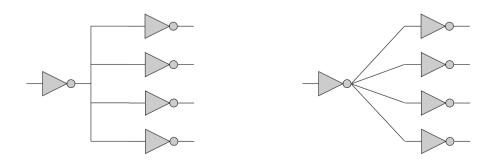

# **Drawing nets**

Three different drawings of the same net (of fan-out 4). We may draw a net in any way that we find convenient or aesthetic. The interpretation of the drawing is that terminals that are connected by lines or curves constitute a net.

# **Digital signals for nets**

We would like to define the digital signal N(t) for a whole net N.

Noise creates different analog signals along the net. Define N(t) to logical only if there is a consensus among all the digital interpretations of analog signals at different terminals of the net. In other words:

- N(t) is zero if the digital values of all the analog signals along the net are zero.

- N(t) is one if the digital values of all the analog signals along the net are one.

- If there is no consensus, then N(t) is non-logical.

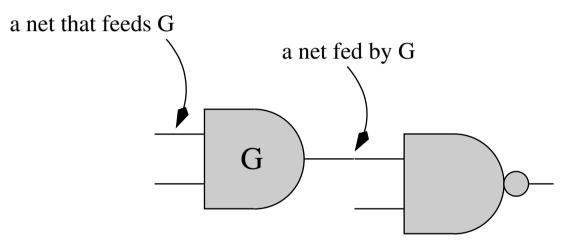

### **Directions in nets**

A net N feeds an input terminal t if the input terminal t in N. A net N is fed by an output terminal t if t is in N.

Information is "supplied" by output terminals and is "consumed" by input terminals.

In "pure" CMOS gates, output terminals are connected via resistors either to the ground (low voltage) or to the power (high voltage). Input terminals are connected only to capacitors.

# **Simple nets**

**Def:** A net *N* is simple if:

- 1. N is fed by exactly one output terminal, and

- 2. N feeds at least one input terminal.

- Consider a simple net  $N = \{t_{out}, t_1, t_2, \dots, t_k\}$ , where  $t_{out}$  is an output terminal, and  $\{t_i\}_{i=1}^k$  are input terminals.

- N can be modeled by a "star" of wires  $\{w_i\}_{i \in I}$ . Each wire  $w_i$  connects  $t_{out}$  and  $t_i$ . We may regard each wire  $w_i$  as a directed edge  $t_{out} \rightarrow t_i$ .

#### **Directed graph corresponding to simple nets**

If every every net N in a circuit C is simple, then we can model C by a directed graph.

- $\blacksquare$  *DG*(*C*) a directed graph.

- Nodes gates of *C*.

- Directed edges directed edge u → v if there is a net N such that: (i) an output terminal of gate u feeds N, and (ii) an input terminal of v is fed by N.

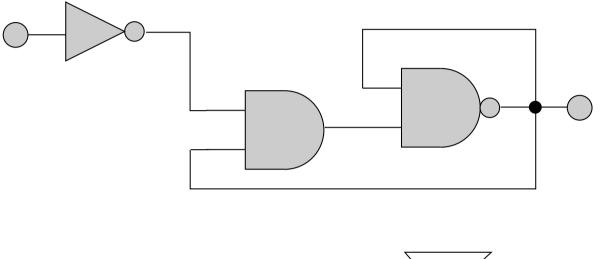

#### **Example of a circuit** C and a directed graph DG(C)

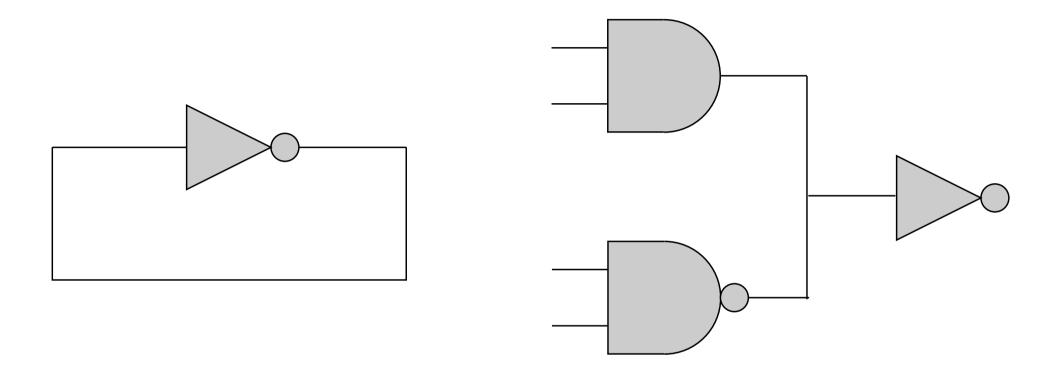

#### Are these circuits combinational circuits?

## Input gates & output gates

Input and output gates model communication with the "external world". Solve the problem of "hanging" wires.

Input Gate

Output Gate

input gate - a gate with zero inputs and a single output.

output gate - a gate with one input and zero outputs.

#### **Syntactic definition of combinational circuits**

**Def:** A combinational circuit is a pair  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  that satisfies the following conditions:

- 1.  $\mathcal{G}$  is a set of gates.

- 2.  $\mathcal{N}$  is a set of nets over terminals of gates in  $\mathcal{G}$ .

- 3. Every terminal t of a gate  $G \in \mathcal{G}$  belongs to exactly one net  $N \in \mathcal{N}$ .

- 4. Every net  $N \in \mathcal{N}$  is simple.

- 5. The directed graph DG(C) is acyclic.

## **Syntactic definition - remarks**

Definition of combinational circuits is independent of the gate types (e.g. inverter, NAND-gate, etc.). The question of whether a circuit is combinational is a purely topological question (i.e. are the interconnections between gates legal?).

syntax - "grammar" rules for forming compound circuits from simple circuits.

### Back to "bad" examples...

Which conditions in the syntactic definition of combinational circuits are violated by the "bad" circuits?

Question: Design an efficient algorithm to check if a given circuit is combinational.

#### **Combinational circuits: Syntax** $\Rightarrow$ **Semantics**

- Completeness: for every Boolean function B, there exists a combinational circuit that implements B (exercise).

- Soundness: every combinational circuit implements a Boolean function. (NP-Complete to decide if a given combinational circuit ever outputs a 1.)

- Simulation: given the digital values of the inputs of a combinational circuit, one can simulate the circuit in time that is linear in the circuit's size.

- Delay analysis: given the propagation delays of all the gates in a combinational circuit, one can compute in linear time the propagation delay of the circuit (upper bound).

#### **Simulation theorem of combinational circuits**

$\blacksquare C = \langle \mathcal{G}, \mathcal{N} \rangle$  - a combinational circuit with k input gates.

- $\{x_i\}_{i=1}^k$  digital input signals

- $[t_1, t_2]$  a sufficiently long interval of time.

Theorem: If the digital signals  $\{x_i(t)\}_{i=1}^k$  are stable during the interval  $[t_1, t_2]$ , then, for every net  $N \in \mathcal{N}$  there exist:

1. a Boolean function  $B_N : \{0,1\}^k \rightarrow \{0,1\}$ , and

2. a propagation delay

$$t_{pd}(N)$$

such that

$$N(t) = B_N(x_1(t), x_2(t), \dots, x_k(t)),$$

for every  $t \in [t_1 + t_{pd}(N), t_2]$ .

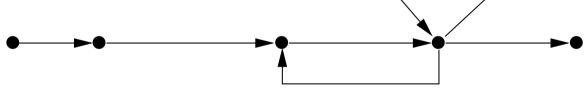

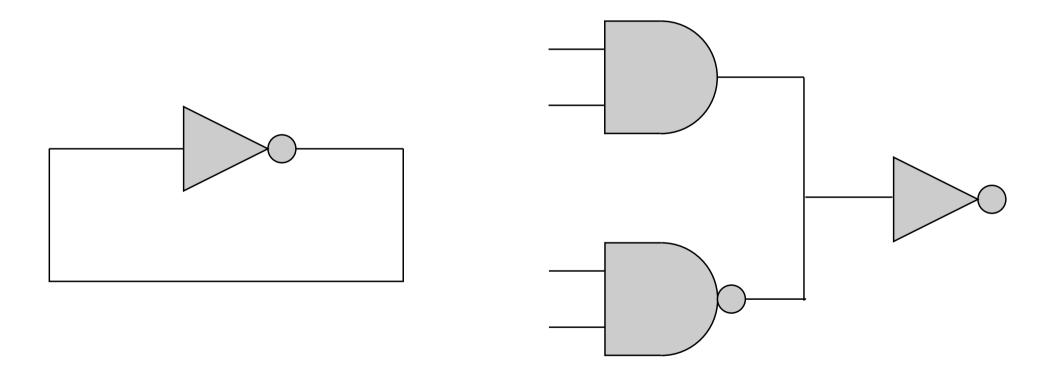

#### **Example - simulation of combinational circuit**

- process nets according to topological order (i.e. u before v if there is an edge  $u \rightarrow v$  in DG(C)).

- assign Boolean function to each net.

- **assign**  $t_{pd}$  to each net.

### **Proof of Simulation Theorem**

Notation:

- $\vec{x}(t)$  the vector  $x_1(t), \ldots, x_k(t)$ .

- $v_1, v_2, \ldots, v_n$  topological order of vertices (gates) in DG(C).

- WLOG:  $v_1, \ldots, v_k$  are the input gates.

- $x_i(t)$  is the digital signal output by  $v_i$  (for  $1 \le i \le k$ ).

- $\bullet$   $e_i$  nets fed by gate  $v_i$  (assume only one).

- $\bullet$   $e_1, e_2, \ldots, e_m$  ordering of the nets in  $\mathcal{N}$ .

- Note that  $e_1$  is fed by  $v_1, \ldots, e_k$  is fed by  $v_k$ , hence  $e_1 = x_1, \ldots, e_k = x_k$ .

## **Proof - Induction hypothesis**

For every  $i \leq m'$  there exist:

- **1.** a Boolean function  $B_{e_i} : \{0, 1\}^k \to \{0, 1\}$ , and

- 2. a propagation delay  $t_{pd}(e_i)$

such that the network  $e_i$  implements the Boolean function

$$B_{e_i}: \{0,1\}^k \to \{0,1\}$$

with propagation delay  $t_{pd}(e_i)$ .

### **Proof - Induction basis**

Instead of proving for m' = 1, we prove for m' = k.

Consider an  $i \le k$ . The net  $e_i$  is fed by  $v_i$ , and the digital signal corresponding to  $e_i$  is  $x_i(t)$ .

$\implies$  define

$$B_{e_i}(\sigma_1, \dots, \sigma_k) = \sigma_i.$$

$$t_{pd}(e_i) = 0.$$

now to induction step...

# **Proof - Induction step**

Ind. Hyp. $(m') \implies$  Ind. Hyp.(m'+1).

Focus on  $e_{m'+1}$ :

- Let  $v_i$  denote the gate that feeds  $e_{m'+1}$ .

- For simplicity: assume that  $v_i$  has 2 inputs fed by the nets  $e_j \& e_k$ , respectively. Also, assume that  $v_i$  has a single output.

- Topological ordering  $\Rightarrow j, k \leq m'$ .

- Ind. Hyp. ⇒:

- $e_j$  implements a Boolean function  $B_{e_j}$  with  $t_{pd}(e_j)$ .

- $e_k$  implements a Boolean function  $B_{e_k}$  with  $t_{pd}(e_k)$ .

- $\blacksquare$   $\Rightarrow$  both inputs to gate  $v_i$  are stable during the interval

$[t_1 + \max\{t_{pd}(e_j), t_{pd}(e_k)\}, t_2].$

# **Proof - Ind. step - cont.**

- Gate  $v_i$  implements a Boolean function  $B_{v_i}$  with propagation delay  $t_{pd}(v_i)$ .

- $\blacksquare \Rightarrow$  the output of gate  $v_i$  equals

$B_{v_i}(B_{e_j}(\vec{x}(t)), B_{e_k}(\vec{x}(t)))$

during the interval

$$[t_1 + \max\{t_{pd}(e_j), t_{pd}(e_k)\} + t_{pd}(v_i), t_2].$$

Define

$$B_{e_{m'+1}}(\vec{\sigma}) = B_{v_i}(B_{e_j}(\vec{\sigma}), B_{e_k}(\vec{\sigma})).$$

$$t_{pd}(e_{m'+1}) = \max\{t_{pd}(e_j), t_{pd}(e_k)\} + t_{pd}(v_i).$$

# **Simulation theorem - Corollaries**

- simulation algorithm

- timing analysis algorithm

- may regard a combinational circuit as a "macro-gate". All instances of the same combinational circuit implement the same Boolean function and have the same propagation delay.

very simple algorithms...

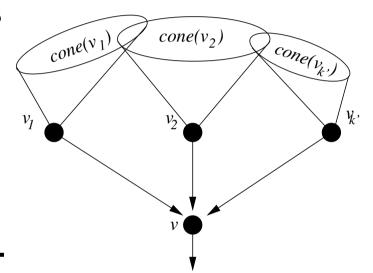

#### **Simulation and timing-analysis algorithm**

- **construct the directed graph** DG(C).

- sort gates in topological order.

- order the nets  $e_1, e_2, \ldots, e_m$ .

- For i = 1 to m do:

Let v<sub>j</sub> denote the gate that feeds e<sub>i</sub>.

$$val(e_i) \leftarrow B_{v_j} \left( \{val(e_k)\}_{e_k \text{ feeds } v_j} \right)$$

$$t_{pd}(e_i) \leftarrow t_{pd}(v_j) + \max\{t_{pd}(e_k)\}_{e_k \text{ feeds } v_j}.$$

Complexity: linear if each gate has a single output terminal and computing  $B_{v_i}$  requires constant time. (why?)

## **Quality measures of combinational gates**

- Suppose C<sub>1</sub> and C<sub>2</sub> are combinational circuits that compute the same Boolean function. How do we decide which one is better? We use two criteria:

- Cost

- Propagation delay

## Cost

We associate a cost with every gate. We denote the cost of a gate G by c(G).

**Def**: The cost of a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  is defined by

$$c(C) \stackrel{\triangle}{=} \sum_{G \in \mathcal{G}} c(G).$$

Remark: Naive cost measure - ignores wiring. The more interesting measure is area. However, computing the area requires detailed physical design (which is hard to compute and is very sensitive to technology).

# **Propagation delay**

We associate a propagation delay with every gate. We denote the propagation delay of a gate G by  $t_{pd}(G)$ .

Def: The propagation delay of a combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  is defined by

$$t_{pd}(C) \stackrel{\triangle}{=} \max_{N \in \mathcal{N}} t_{pd}(N).$$

We often refer to the propagation delay of a combinational circuit as its depth or simply its delay.

### **Delays of paths**

■ path - a sequence  $p = \{v_0, v_1, \dots, v_k\}$  of gates that form a path in the directed graph DG(C).

$\blacksquare$  delay of a path p -

$$t_{pd}(p) = \sum_{v \in p} t_{pd}(v).$$

#### Claim:

$$t_{pd}(C) = \max\{t_{pd}(p) \mid \text{paths } p\}.$$

critical path - a path p that satisfies  $t_{pd}(p) = t_{pd}(C)$ .

Q: Number of paths can be exponential. How were we able to compute  $max\{t_{pd}(p) : paths p\}$ ?

# **Example: gate costs and delays**

Müller and Paul compiled the following costs and delays of gates. These figures were obtained by considering ASIC libraries of two technologies and normalizing them with respect to the cost and delay of an inverter.

| Gate      | Motorola |       | Venus |       |

|-----------|----------|-------|-------|-------|

|           | cost     | delay | cost  | delay |

| INV       | 1        | 1     | 1     | 1     |

| AND,OR    | 2        | 2     | 2     | 1     |

| NAND, NOR | 2        | 1     | 2     | 1     |

| XOR, NXOR | 4        | 2     | 6     | 2     |

| MUX       | 3        | 2     | 3     | 2     |

# Syntax & Semantics

semantics - function that a circuit implements. Also called functionality or even the behavior of the circuit.

In general, formal description that relates

input values  $\mapsto$  output values.

In non-combinational circuits, the output depends not only on the current inputs, so semantics cannot be described simply by a Boolean function.

- syntax a formal set of rules that govern how "grammatically correct" circuits are constructed from smaller circuits (just as words form sentences).

- syntax  $\neq \Rightarrow$  useful circuit (e.g. adder).

- syntax => well defined functionality, simple simulation, & simple timing analysis.

# **Summary**

gates - implement simple Boolean functions

- nets & wires used to connect terminals of gates

- formal (syntactic) definition of combinational circuits

- combinational gates are easy to:

- recognize

- simulate

- analyze (propagation delay)

- quality criteria: cost & delay

# **Chapter 3: Trees** *Computer Structure - Spring 2007*

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary Questions**

- Which Boolean functions are suited for implementation by tree-like combinational circuits?

- In what sense are tree-like implementations optimal?

## Goals

- define associative Boolean functions (and classify them).

- trees combinational circuits that implement associative Boolean funcs.

- analyze delay & cost of trees.

prove optimality.

# **Associative dyadic boolean functions**

**Def:** A Boolean function  $f : \{0, 1\}^2 \rightarrow \{0, 1\}$  is associative if

$$f(f(\sigma_1, \sigma_2), \sigma_3) = f(\sigma_1, f(\sigma_2, \sigma_3)),$$

for every  $\sigma_1, \sigma_2, \sigma_3 \in \{0, 1\}$ .

Q: List all the associative Boolean functions

$$f: \{0,1\}^2 \to \{0,1\}.$$

"A": There are 16 dyadic Boolean functions, only need to list them and check...

$$f_n$$

: composing  $f : \{0, 1\}^2 \to \{0, 1\}$

Def: Let  $f : \{0,1\}^2 \to \{0,1\}$  denote a Boolean function. The function  $f_n : \{0,1\}^n \to \{0,1\}$ , for  $n \ge 2$  is defined by induction as follows.

1. If n = 2 then  $f_2 \equiv f$ .

2. If n > 2, then  $f_n$  is defined based on  $f_{n-1}$  as follows:

$$f_n(x_1, x_2, \dots, x_n) \stackrel{\triangle}{=} f(f_{n-1}(x_1, \dots, x_{n-1}), x_n).$$

Example:

$$NOR_4(x_1, x_2, x_3, x_4) = NOR(NOR(NOR(x_1, x_2), x_3), x_4).$$

Note that NOR is not associative!

# $f_n$ : the associative case

If  $f(x_1, x_2)$  is associative, then parenthesis are not important. Formally:

Claim: If  $f : \{0,1\}^2 \rightarrow \{0,1\}$  is an associative Boolean function, then for every  $k \in [2, n-2]$ :

$f_n(x_1, x_2, \dots, x_n) = f(f_k(x_1, \dots, x_k), f_{n-k}(x_{k+1}, \dots, x_n)).$

**Q**: Show that the set of functions  $f_n(x_1, \ldots, x_n)$  that are induced by associative dyadic Boolean functions is

{constant 0, constant  $1, x_1, x_n, \text{AND}_n, \text{OR}_n, \text{XOR}_n, \text{NXOR}_n$ }.

**Remark**: Only last 4 functions are "interesting". We focus on  $OR_n$ .

# **Definition of OR-trees**

**Def**: A combinational circuit  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  that satisfies the following conditions is called an **OR-tree**(*n*).

- **1. Input:** x[n-1:0].

- **2. Output:**  $y \in \{0, 1\}$

- 3. Functionality:  $y = OR(x[0], x[1], \dots, x[n-1])$ .

- 4. Gates: All the gates in  $\mathcal{G}$  are or-gates.

- 5. **Topology:** The underlying graph of DG(C) (i.e. undirected graph obtained by ignoring edge directions) is a tree.

- Note that in the tree:

- leaves correspond to the inputs x[n-1:0] and the output y.

- interior nodes OR-gates.

- Could root the tree, and then the root is the output.

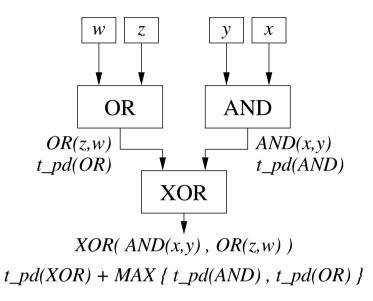

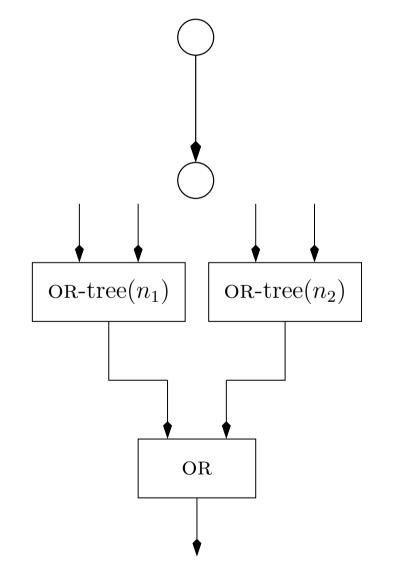

# **Recursive definition of OR-trees**

**Def**: an **OR-tree**(n) is defined recursively as follows:

**basis:** (n = 1) - a trivial circuit in which input directly feeds output.

step: (n > 1) - compose two trees  $T_{n_1} \& T_{n_2}$  by feeding their output to a new gate.

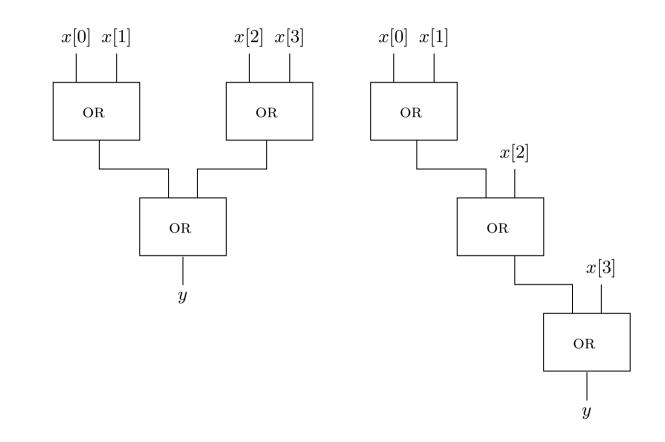

# **Example:** OR-tree(4)

**Cost** - both trees have 3 gates.

Delay - 2 gates vs. 3.

## **Cost of OR-trees**

Claim: The cost of every OR-tree(n) is  $(n-1) \cdot c(OR)$ .

**Proof**: By induction on n.

Induction basis: n = 2. In this case, or-tree(2) contains a single or-gate. What about n = 1?

# **Cost of OR-trees - Induction step**

- let C denote an OR-tree(n).

- **I** let g denote the OR-gate that outputs the output of C.

- $\blacksquare$  g is fed by two wires  $e_1$  and  $e_2$ .

- $\blacksquare$   $e_1$  is the output of  $C_1$  an or-tree $(n_1)$

- $\blacksquare e_2$  is the output of  $C_2$  an or-tree $(n_2)$

$$\blacksquare n_1 + n_2 = n$$

■ Ind. Hyp.

$$\Rightarrow c(C_1) = (n_1 - 1) \cdot c(\text{OR})$$

&  $c(C_2) = (n_2 - 1) \cdot c(\text{OR})$ .

$$c(C) = c(g) + c(C_1) + c(C_2)$$

=  $(1 + n_1 - 1 + n_2 - 1) \cdot c(OR)$

=  $(n - 1) \cdot c(OR)$ . QED

# **Delay of OR-trees**

Since all gates in an OR-tree are identical, delay of tree is proportional to the length of longest path from input to output (i.e., depth of tree).

**DEF**: A rooted tree is a minimum depth tree if its depth is minimum among all the rooted trees with the same number of leaves.

Since all trees with n inputs have the same cost, we may focus on min. depth trees.

Question: How many min. depth trees are there with  $n = 2^k$  inputs?

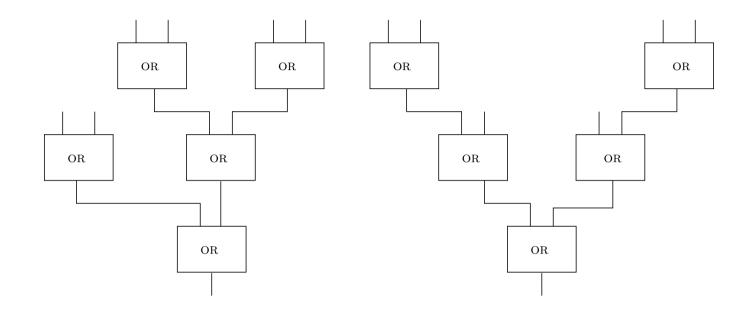

# **Example: delay of OR-trees**

Question: Are these min. depth trees?

# Lower bound on depth

Question: Prove that if  $T_n$  is a rooted binary tree with n leaves, then the depth of  $T_n$  is at least  $\lceil \log_2 n \rceil$ .

# **Upper bound on depth**

- Wish to present a simple procedure for constructing  $T_n$  with depth  $\lceil \log_2 n \rceil$ .

- Natural candidate: balanced trees...

**DEF:** Two positive integers a, b are a balanced partition of n if: (1) a + b = n, and (2)  $\max\{\lceil \log_2 a \rceil, \lceil \log_2 b \rceil\} \le \lceil \log_2 n \rceil - 1$ .

**Example:** Suppose n = 6. In this case  $\lceil \log_2 n \rceil = 3$ . Hence a = b = 3 is a balanced partition, but so is a = 4, b = 2.

#### **Procedure for constructing "balanced" trees**

Question: Consider the following recursive algorithm for constructing a binary tree  $T_n$  with  $n \ge 2$  leaves. Prove that the depth of  $T_n$  is  $\lceil \log_2 n \rceil$ .

- 1. The case that  $n \le 2$  is trivial (two leaves connected to a root).

- 2. If n > 2, then let a, b be balanced partition of n.

- 3. Compute trees  $T_a$  and  $T_b$ . Connect their roots to a new root to obtain  $T_n$ .

# **Are balanced** OR-trees optimal?

What is the best (min. cost & delay) choice of a topology for a combinational circuit that implements the Boolean function OR<sub>n</sub>? Is a tree indeed the best topology?

Could one do better if another implementation is used?

# **Optimality of balanced OR-trees**

Would like to prove that every combinational circuit C that implements  $OR_n$  satisfies:

$c(C) \ge n - 1$  $t_{pd}(C) \ge \log_2 n.$

We need to be more accurate about the model:

**Q:** what is the cost/delay of an *n*-input OR-gate?

assumption 1: the fan-in of every gate  $\leq 2$ , so we have to build big gates from basic gates.

assumption 2: the cost & delay of every basic gate is  $\geq 1$ . (input/output gates are free)

# **Optimality of balanced OR-trees**

Would like to prove that every combinational circuit C that implements  $OR_n$  satisfies:

$c(C) \ge n - 1$  $t_{pd}(C) \ge \log_2 n.$

Looking for proof also for the case that DG(C) is not a tree!

## **Restriction of a Boolean function**

Def: Let  $f : \{0,1\}^n \to \{0,1\}$  denote a Boolean function. Let  $\sigma \in \{0,1\}$ . The Boolean function  $g : \{0,1\}^{n-1} \to \{0,1\}$  defined by

$$g(w_0,\ldots,w_{n-2}) \stackrel{\triangle}{=} f(w_0,\ldots,w_{i-1},\sigma,w_i,\ldots,w_{n-2})$$

is called the restriction of f with  $x_i = \sigma$ . We denote it by  $f_{\uparrow x_i = \sigma}$ .

Examples:

$$\operatorname{XOR}_{\restriction x_2=1}(x_1) \stackrel{\scriptscriptstyle \bigtriangleup}{=} \operatorname{XOR}(x_1,1)$$

$$\mathsf{MAJORITY}_{\upharpoonright x_n=1}(x_1,\ldots,x_{n-1}) \triangleq \begin{cases} 1 & \text{if } \sum_{i=1}^{n-1} x_i + 1 > n/2 \\ 0 & \text{otherwise.} \end{cases}$$

# **Cone of a Boolean function**

A boolean function  $f : \{0, 1\}^n \rightarrow \{0, 1\}$  depends on its *i*th input if

$$f_{\restriction x_i=0} \not\equiv f_{\restriction x_i=1}.$$

**Def**: The **cone** of a Boolean function f is defined by

$cone(f) \stackrel{\triangle}{=} \{i : f \text{ depends on its } i \text{th input}\}.$

Claim: The Boolean function  $OR_n$  depends on all its inputs, namely

$|\operatorname{cone}(\operatorname{or}_n)| = n.$

# **Input-Output reachability**

Claim: If a combinational circuit C implements a Boolean function f, then there must be a path in DG(C) from every input in cone(f) to the output of C.

Proof: by contradiction,

**assume**  $i \in cone(f)$ .

- let  $g_i \in \mathcal{G}$  denote the input gate that feeds the *i*th input.

- assume that in DG(C) there is no path from  $g_i$  to the output y.

- **show that** C does not implement f.

# **Input-Output reachability - cont.**

Find vectors  $w', w'' \in \{0, 1\}^n$  such that

$$f(w') \neq f(w'')$$

$$w'[i] \neq w''[i]$$

$$.w'[j] = w''[j], \text{ for every } j \neq i$$

Proof of Simulation Algorithm

$\Rightarrow$  C outputs the same value in y when input w' and w''.

$\Rightarrow$  C errs either with w' or with w''. QED

# Linear Cost Lower Bound Theorem assumptions:

- fan-in of every gate at most 2.

- cost of trivial gates (i.e. input/output gates) is zero.

cost of non-trivial gate is at least 1.

**Theorem:** If C is a combinational circuit that implements a Boolean function f, then

$c(C) \ge |\operatorname{cone}(f)| - 1.$

Corollary: If  $C_n$  is a combinational circuit that implements  $OR_n$ , then  $c(C_n) \ge n - 1$ .

Easy to prove theorem for trees, but what about arbitrary DAGs?

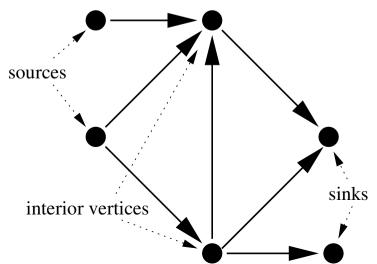

# **DAG terminology**

Consider the directed acyclic graph (DAG) DG(C).

- $\deg_{in}(v)$ : in-degree of a vertex v is the number of edges that enter the vertex v.

- $\deg_{out}(v)$ : out-degree of a vertex v: is the number of edges that emanate from the vertex v.

- source a vertex with in-degree zero.

- sink a vertex with out-degree zero.

- interior vertex a vertex that is neither a source or a sink.

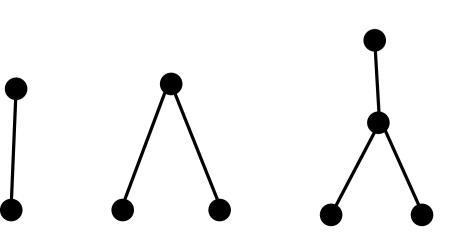

### **Leaves and interior vertices in trees**

- Let T = (V, E) denote a tree with at least two vertices.

- A leaf is a vertex of degree 1.

- An interior vertex is a vertex that is not a leaf.

- leaves(V) set of leaves in V.

- **interior**(V) set of interior vertices in V.

- Claim:

If the degree of every vertex in T is at most three, then

$|\text{interior}(V)| \ge |\text{leaves}(V)| - 2.$

#### **Underlying graph of** DG(C)

$\blacksquare C$  - a combinational circuit & DG(C) = (V, A) - a DAG

- underlying graph of DG(C) undirected graph G = (V, E), where  $(u, v) \in E \Leftrightarrow (u \to v) \in A$ .

- If fan-in of every gate in C is at most 2 and G is a tree, then degree of every vertex in G is at most 3.

- Leaves in *G* correspond to input and output gates in *C*.

Interior vertices in G correspond to non-trivial gates in C.

Case of a tree:

Claim: Assume *C* has *n* inputs and a single output. Assume fan-in of all gates is at most 2. If *G* is a tree, then

$c(C) \ge n - 1.$

#### **Proof of linear cost lower bound theorem**

- If underlying graph of DG(C) is a tree, then previous claim proves the theorem.

- If DG(C) = (V, E) is not a tree, then construct a directed "binary tree" T' = (V', E') such that

- $V' \subseteq V \& E' \subseteq E$

- $\blacksquare \operatorname{sources}(T') = \operatorname{cone}(f)$

- output gate  $\in V'$ .

- in T' we have |interior nodes|  $\geq$  |sources| -1.

- But interior nodes of T are also interior in DG(C), and number of sources in T equals |cone(f)|. QED.

Left to show how *T* is constructed...

## Construction of T

## larger fan-in

Q: Generalize the lower bound on the cost to the case that the fan-in of every gate is bounded by a constant k.

#### **Logarithmic Delay Lower Bound Theorem**

Theorem: Let  $C = \langle \mathcal{G}, \mathcal{N} \rangle$  denote a combinational circuit that implements a non-constant Boolean function  $f : \{0, 1\}^n \to \{0, 1\}$ . If the fan-in of every gate in  $\mathcal{G}$  is at most k, then the delay of C is at least  $\log_k |cone(f)|$ .

**Corollary:** Let  $C_n$  denote a combinational circuit that implements  $OR_n$ . Let k denote the maximum fan-in of a gate in  $C_n$ . Then

$t_{pd}(C_n) \ge \lceil \log_k n \rceil.$

# **Proof of logarithmic lower bound**

• deal only with the graph DG(C).

- show that exists a path with at least  $\log_k |cone(f)|$  interior vertices in DG(C).

- why interior?

- input/output gates and constants have zero delay  $\Rightarrow$  should not be counted.

- only sources & sinks have zero delay ⇒ count interior vertices.

- cone(v) set of sources from which v is reachable. Note that  $|cone(output)| \ge |cone(f)|$ .

- d(v) max number of interior vertices along a path from a source in *cone*(v) to v (including v).

• suffice to prove that  $d(v) \ge \log_k |cone(v)|$ .

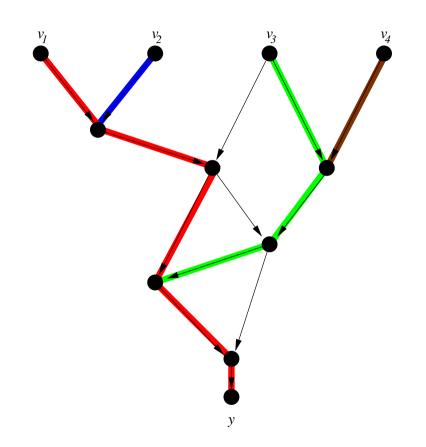

# **Proof:** $d(v) \ge \log_k |cone(v)|$

Proof by induction on d(v).

- Basis: d(v) = 0. In this case v is a source, |cone(v)| = 1.

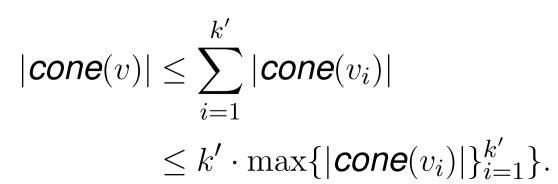

- Step: d(v) = i + 1. Edges entering v are

$$v_1 \rightarrow v, \ldots, v_{k'} \rightarrow v$$

, for  $k' \leq k$ .

**by def:**

$$d(v) = \max\{d(v_i)\}_{i=1}^{k'} + 1$$

• cone

$$(v) = \bigcup_{i=1}^{k'} cone(v_i).$$

**Cont. proof:**  $d(v) \ge \log_k |cone(v)|$ Let v' denote a predecessor of v that satisfies

$|cone(v')| = \max\{|cone(v_i)|\}_{i=1}^{k'} \ge |cone(v)|/k'.$

The induction hypothesis implies that

$d(v') \ge \log_k |cone(v')|.$

But,

$d(v) \ge 1 + d(v')$   $\ge 1 + \log_k |cone(v')|$   $\ge \log_k k + \log_k |cone(v)|/k'$  $\ge \log_k |cone(v)|.$

# Cont. proof: $d(v) \ge \log_k |cone(v)|$

Finally, we deal with the case that v is a sink.

- $\blacksquare v$  has a unique predecessor v'.

- we have d(v) = d(v') and cone(v) = cone(v').

- **induction step applies to** v', and hence we have

$d(v) \ge \log_k |cone(v)|,$

as required.

## **Summary**

associative Boolean functions.

- **\blacksquare** extend dyadic functions to functions with n arguments.

- only four non-trivial associative Boolean functions.

- OR-tree(n) combinational circuits that implement ORn using a topology of a tree.

- cost(or-tree) = n 1.

- $t_{pd}(\text{balanced or-tree}) = \log_2 n$ .

- Balanced OR-trees optimal cost & delay.

- two lower bounds:

- $\operatorname{cost} \ge |\operatorname{cone}(f)| 1.$

- $\bullet t_{pd} \ge \log_k |cone(f)|.$

## Chapter 4: Decoders & Encoders Computer Structure - Spring 2007

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary questions**

- Suggest methods for designing combinational circuits that implement nontrivial Boolean functions.

- How do we check if a design of a combinational circuit is correct?

### Goals

- vector notation: buses, indexed signals, multiple copies of gates

- representation: binary representation

- Decoders:

- definition (specification)

- implementation

- correctness proof

- analyze delay & cost

- optimality

- Encoders: same ritual... (definition (specification), correctness proof, analyze delay & cost, optimality)

#### **Parallel nets**

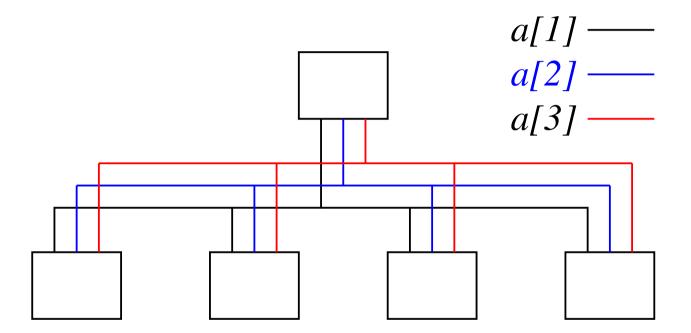

We could use separate names for each net:

# **Indexing parallel nets**

We could index the names of the nets:

### **Bus notation**

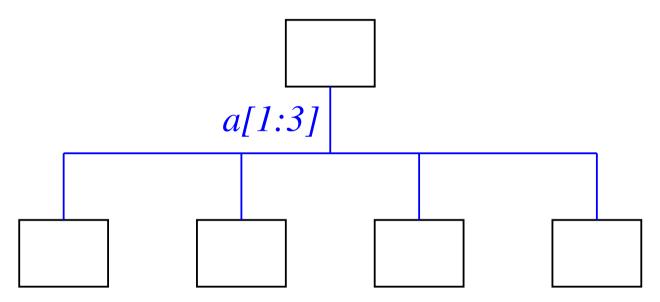

We could refer to the nets as a bus a[1:3]:

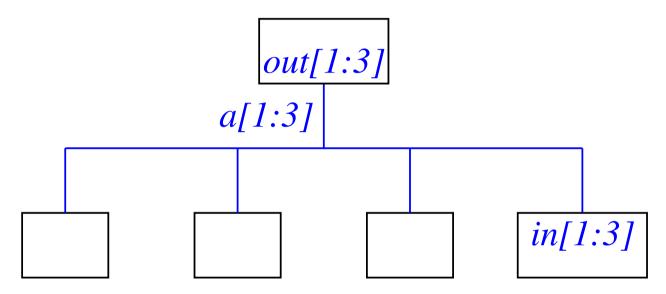

To make sense we would have to give indexed names to inputs/output terminals.

For example: input terminals in[1:3] and output terminals out[1:3]. And then a[i] feeds in[i] and is fed by out[i].

#### **Bus notation**

Indexes of terminal names match indexes of bus names:

#### **Bus related definitions**

- bus set of nets that are connected to the same modules.

- bus width number of nets in the bus.

**Example:** The bus a[1 : 3] connects the output terminals out[1 : 3] to the input terminals in[1 : 3]. The width is 3.

#### **Indexed buses**

- Assignment  $in[1:4] \leftarrow out[1:4]$  means  $in[1] \leftarrow out[1], \dots, in[4] \leftarrow out[4]$ .

- **Reversing**  $in[1:4] \leftarrow out[4:1]$  means  $in[1] \leftarrow out[4], \dots, in[4] \leftarrow out[1]$ .

- Hardwired shifting  $in[i:j] \leftarrow out[i+5:j+5]$  means  $in[i] \leftarrow out[i+5], \dots, in[j] \leftarrow out[j+5]$ .

### **Bus assignment conventions**

Unless stated explicitly, reversing is not used. The assignments:

$$b[i:j] \leftarrow a[i:j]$$

&  $b[j:i] \leftarrow a[i:j]$

have the same meaning (so we don't have to worry about ascending/descending indexes).

Hardwired-shifting is used for shifted index ranges. For example,

$$b[i+5:j+5] \leftarrow a[i:j]$$

means

$$b[i+5] \leftarrow a[i] \quad b[i+6] \leftarrow a[i+1] \quad \cdots \quad b[j+5] \leftarrow a[j]$$

## **Signals on buses**

- **Consider a bus** a[5:1].

- The signal on a[3] at time t is a[3](t).

- Abbreviate and simply write a[3] as the signal on a[3] after it stabilizes.

- Similarly: a[5:1] refers both to the bus and to the stable signal on the bus.

- $\blacksquare \implies a[5:1]$  is both a bus and a binary string.

- Abbreviate a[5:1] and write  $\vec{a}$  if index range is clear from context.

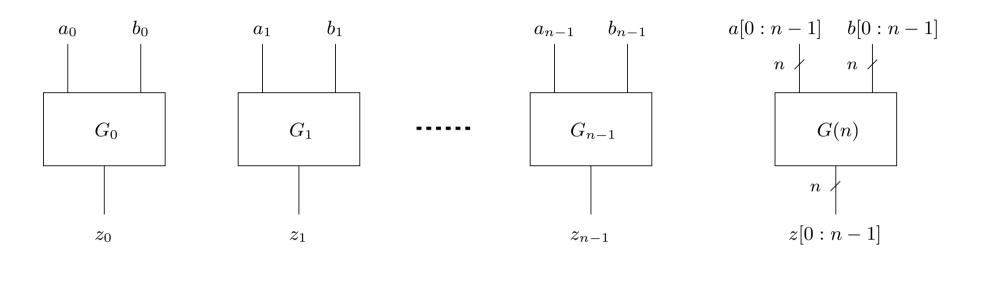

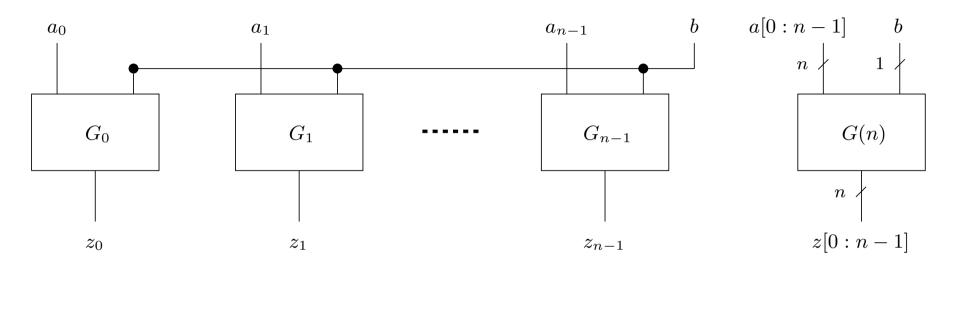

## multiple instances of the same gate

$(\mathbf{A})$ (B)

- $\blacksquare$   $G_i$  the *i*th instance of gate G in G(n).

- $\blacksquare$   $a_i, b_i$  the two input terminals of  $G_i$ .

$\blacksquare$   $z_i$  - the output terminal of  $G_i$ .

# **Common input in** G(n)

*b* is fed to the second input terminal of all the gates.

(A) (B)

Fanout of the net b is n. In practice, a large fanout increases the capacity of a net and causes an increase in the delay of the circuit. Ignore this phenomenon in this course.

## **Concatenation of binary strings**

assume that a and b are binary strings.

- **a**  $\cdot$  **b** the string obtained by concatenating *a* and *b*.

- example: if a = 01 and b = 10, then  $a \cdot b = 0110$ .

•

$$a^i$$

- the string  $\underbrace{a \cdot a \cdots a}_{i \text{ times}}$ .

- example: if a = 01 and i = 3, then  $a^i = 010101$ .

- If A is a set of strings, then  $A^i$  is the set of strings

$$A^i = \{a_1 \cdots a_i : \forall j \le i : a_j \in A\}.$$

• example:  $\{0,1\}^n$  - set of binary strings of length n.

- $A^* \stackrel{\scriptscriptstyle \Delta}{=} \cup_{i=0}^{\infty} A^i$  ( $A^0 = \{\Lambda\}$ , not the empty set).

- $\blacksquare A^+ \stackrel{\scriptscriptstyle \triangle}{=} \cup_{i=1}^{\infty} A^i.$

# Values represented by binary strings

Binary strings can be used to represent numbers. Among the many methods for representing natural numbers:

- Binary representation

- Unary representation

- 1-out-of-n (one-hot).

# **Binary representation**

The value represented in binary representation by a binary string a[n-1:0] is denoted by  $\langle a[n-1:0] \rangle$ . It is defined as follows

$$\langle a[n-1:0] \rangle \stackrel{\scriptscriptstyle riangle}{=} \sum_{i=0}^{n-1} a_i \cdot 2^i.$$

- Could define a function  $\langle \rangle_n : \{0,1\}^n \to [0,2^n-1]$ .

- Usually omit the parameter *n* clear from context.

Inverse function  $bin : [0, 2^n - 1] \to \{0, 1\}^n$ .

$\forall a[n-1:0] \in \{0,1\}^n$ :  $bin_n(\langle a[n-1:0] \rangle) = a[n-1:0].$

# **Division by** $2^k$ **in binary representation**

reminder: division by b with remainder:

$x = q \cdot b + r$ , where  $r \in [0, b - 1]$ .

- **q** quotient equals  $\lfloor x/b \rfloor$

- **r** remainder equals mod(x, b).

- Consider a binary string a[n-1:0] and  $x = \langle a[n-1:0] \rangle$ .

- How do we compute (the binary representation of)  $\lfloor x/2^k \rfloor \& \mod(x, 2^k)$ ?  $r = \langle a[k-1:0] \rangle$   $q = \langle a'[n-k-1:0] \rangle$ , where  $a'[n-k-1:0] \leftarrow a[n-1:k]$  (with shifting).

### **Decoders**

A decoder with input length n is a combinational circuit specified as follows:

```

Input: x[n-1:0] \in \{0,1\}^n.

```

**Output:**  $y[2^n - 1:0] \in \{0,1\}^{2^n}$

Functionality:

$$y[i] = 1 \iff \langle \vec{x} \rangle = i.$$

- |outputs| of a decoder is exponential in |inputs|.

- exactly one bit of the output  $\vec{y}$  is set to one. (called also one-hot encoding or 1-out-of-k encoding.)

- **DECODER**(n) a decoder with input length n

example: DECODER(3) - on input x = 101, the output y equals 00100000.

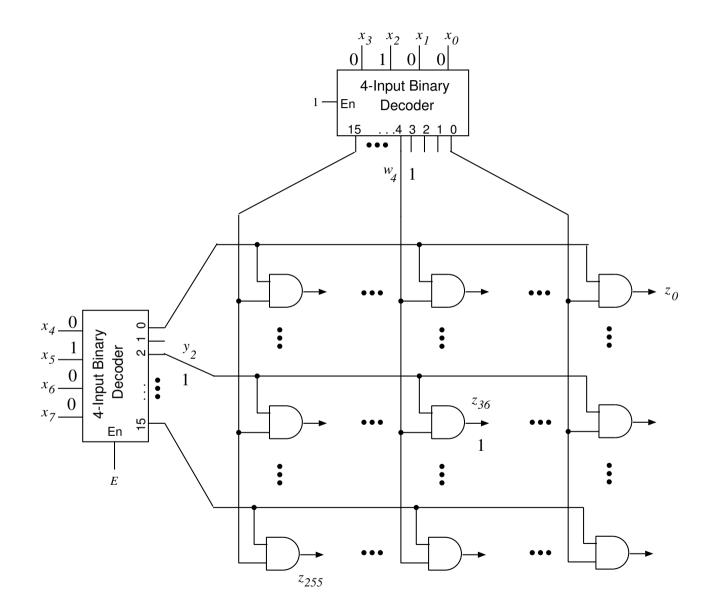

# decoder(8) - schematic

# $\mathsf{DECODER}(n)$ - schematic

#### Weaknesses of standard decoder descriptions

- Why is the design correct?

- Can you prove correctness?

- Can't prove it unless the design is formally defined...

- Is the design (asymptotically) optimal?

- Why partition into n/2 & n/2? Is that the best partition?

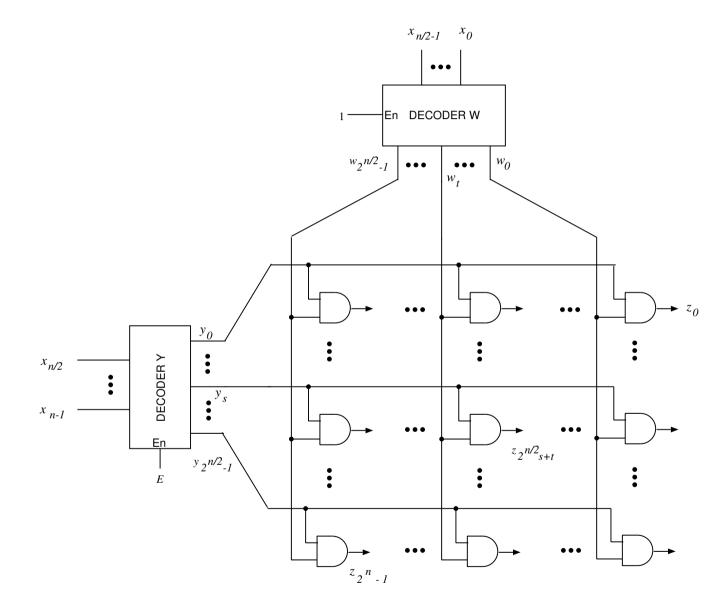

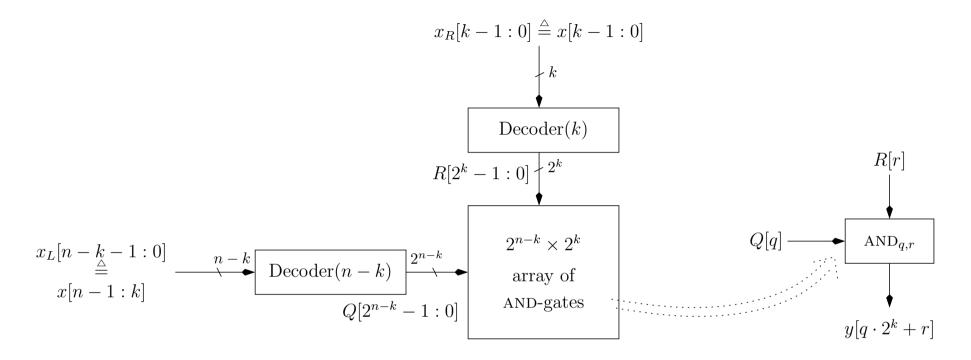

# Formal description of $\mathsf{DECODER}(n)$

Use recursion.

**Basis**: DECODER(1): is simply one inverter where:

$$\begin{split} y[0] &\leftarrow \operatorname{inv}(x[0]) \\ y[1] &\leftarrow x[0]. \end{split}$$

#### Formal description of $\mbox{description}$ - recursive step

## **Correctness proof**

The proof is by induction.

Induction hypothesis for *n*: if DECODER(n) is input x[n-1:0], then the output  $y[2^n - 1:0]$  satisfies:

$$\forall 0 \le i < 2^n : \quad y[i] = 1 \quad \Longleftrightarrow \quad \langle x[n-1:0] \rangle = i.$$

Induction basis: n = 1: trivial.

Induction step: show that:

$[\forall n' < n : \text{ Ind. Hyp. } (n')] \implies \text{ Ind. Hyp. } (n).$

#### induction step - cont.

Fix i ∈ [2<sup>n</sup> − 1 : 0] and prove that y[i] is correct.

Divide by 2<sup>k</sup>: i = q · 2<sup>k</sup> + r.

Ind. Hyp. (k) ⇒

$$R[r] = 1 \iff \langle x_R[k-1:0] \rangle = r.$$

Ind. Hyp.  $(n - k) \Rightarrow$

$$Q[q] = 1 \iff \langle x_L[n - k - 1:0] \rangle = q$$

Now  $y[i] = y[q \cdot 2^k + r]$ , hence

$$y[i] = 1 \iff R[r] = 1 \text{ and } Q[q] = 1$$

$$\iff \langle x_R[k-1:0] \rangle = r \text{ and } \langle x_L[n-k-1:0] \rangle = q.$$

$$\iff \langle x[n-1:0] \rangle = i \quad \mathsf{QED}$$

### **Cost analysis**

The cost c(n) satisfies the following recurrence equation:

$$c(n) = \begin{cases} c(\text{INV}) & \text{if } n=1\\ c(k) + c(n-k) + 2^n \cdot c(\text{AND}) & \text{otherwise.} \end{cases}$$

It follows that

$$c(n) = c(k) + c(n-k) + \Theta(2^n)$$

• Obviously  $c(n) = \Omega(2^n)$ .

- Next slide: for every choice of k,  $c(n) = O(2^n)$ .

- See lecture notes for tight analysis with k = n/2.

#### **Cost analysis - cont.**

**Claim:**  $c(n) = O(2^n)$ .

Proof: Set  $\beta = c(AND)$ , and  $\alpha = \max\{3\beta, c(1)/2, c(2)/4, c(3)/8\}.$ We prove by induction that  $c(n) \leq \alpha \cdot 2^n$ . Induction basis follows for  $n \leq 3$  by definition of  $\alpha$ .

Induction step for  $n \ge 4$ :

$$c(n) = c(k) + c(n - k) + \beta \cdot 2^{n}$$

$$\leq \alpha \cdot 2^{k} + \alpha \cdot 2^{n-k} + \beta \cdot 2^{n}$$

$$\leq \alpha \cdot 2^{n-1} + \alpha \cdot 2 + \beta \cdot 2^{n}$$

$$= 2^{n} \left(\frac{\alpha}{2} + \beta + \frac{2\alpha}{2^{n}}\right).$$

But,

$$\beta \leq \alpha/3, \text{ and}$$

$$n \geq 4 \Rightarrow \frac{2}{2^{n}} \leq \frac{1}{6}.$$

Hence  $c(n) \leq \alpha \cdot 2^{n}.$

## **Delay analysis**

The delay of DECODER(n) satisfies the following recurrence equation:

$$d(n) = \begin{cases} d(\text{INV}) & \text{if } n=1\\ \max\{d(k), d(n-k)\} + d(\text{AND}) & \text{otherwise.} \end{cases}$$

Set k = n/2, and it follows that  $d(n) = \Theta(\log n)$ .

Question: Prove that DECODER(n) is asymptotically optimal with respect to cost and delay.

# Weight of binary strings

Def: The Hamming weight of a binary string is defined by

$$\mathbf{Wt}(a[n-1:0]) \stackrel{\scriptscriptstyle \Delta}{=} |\{i:a[i] \neq 0\}|.$$

Note that

$$wt(a[n-1:0]) = \sum_{i=1}^{n-1} a[i].$$

example:

wt(01101) = 3.

### **Encoders - Definitions**

We define the encoder partial function as follows. Def: The function

$$\mathsf{ENCODER}_n : \{ \vec{y} \in \{0, 1\}^{2^n} : \textit{Wt}(\vec{y}) = 1 \} \to \{0, 1\}^n$$

is defined as follows:

$$Wt(y) = 1 \Longrightarrow y[\langle encoder_n(\vec{y}) \rangle] = 1.$$

Examples:

$ENCODER_2(0100) = 10$  $ENCODER_2(0101) = undefined.$

#### **Encoder - Defs. - cont.**

**ENCODER**(n) - a comb. circuit with  $2^n$  inputs and n outputs that implements the Boolean function ENCODER<sub>n</sub>.

Functionality is not defined for all binary strings.

encoder = decoder<sup>-1</sup>.

#### **Encoders - Defs. - cont.**

${\tt ENCODER}(n)$  can be also specified as follows:

```

Input: y[2^n - 1:0] \in \{0,1\}^{2^n}.

```

**Output:**  $x[n-1:0] \in \{0,1\}^n$ .

Functionality:

$$wt(\vec{y}) = 1 \implies y[\langle \vec{x} \rangle] = 1.$$

If  $wt(\vec{y}) \neq 1$ , then the output  $\vec{x}$  is arbitrary.

examples: Consider an encoder ENCODER(3).

- on input 00100000, the output equals 101.

- on input 01101011, the output is not specified.

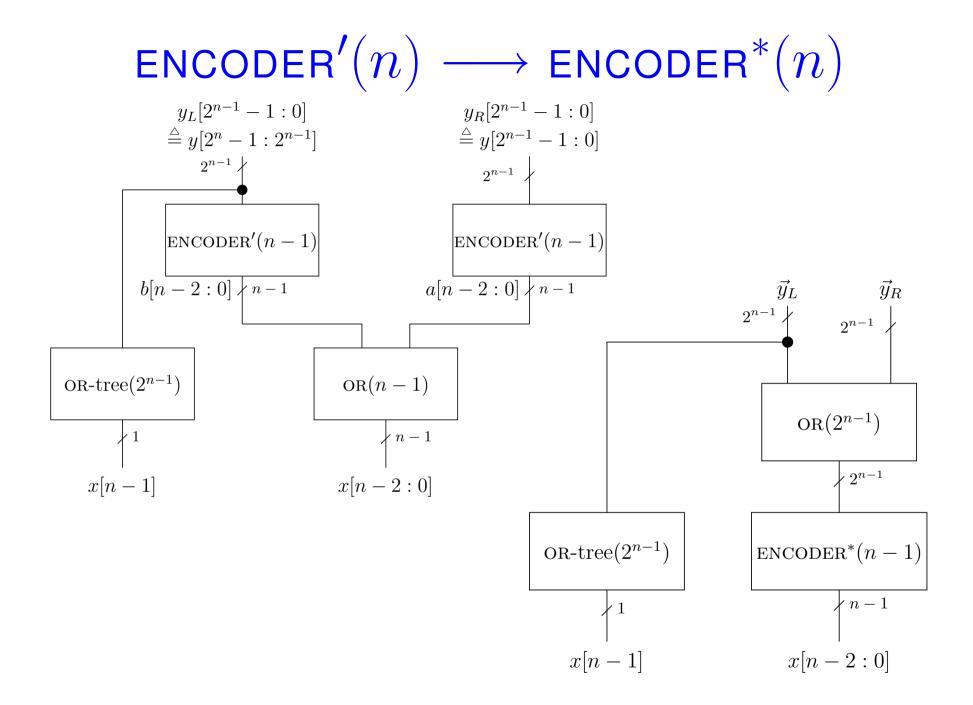

# **Encoder - implementation**

Plan:

**Design a simple encoder** encoder(n).

**Prove correctness of** encoder'(n).

**Improve** ENCODER'(n) to obtain ENCODER\*(n).

Prove functional equivalence

```

\mathrm{encoder}^*(n) \equiv \mathrm{encoder}'(n),

```

and hence, correctness of  $\operatorname{encoder}^*(n).$

**Prove asymptotic optimality of**  $encoder^*(n)$ .

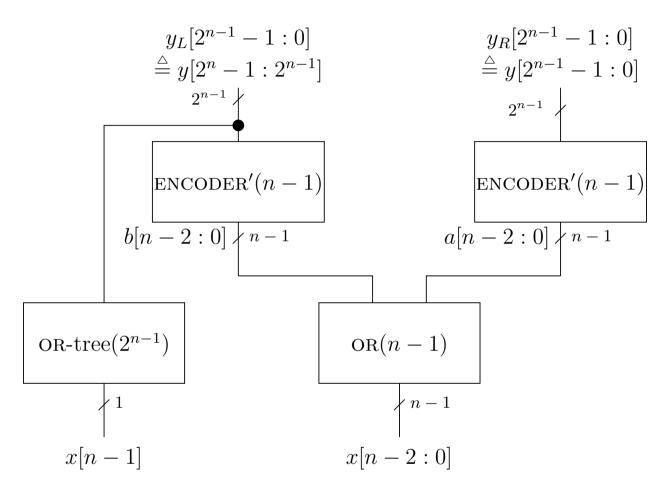

$$\operatorname{encoder}'(n)$$

Use recursion.

**Basis:** ENCODER(1): is simply  $x[0] \leftarrow y[1]$  (zero cost, zero delay).

**Recursion step:** Partition input  $y[2^n - 1:0]$

$$y_L[2^{n-1} - 1:0] = y[2^n - 1:2^{n-1}]$$

$$y_R[2^{n-1} - 1:0] = y[2^{n-1} - 1:0].$$

Apply encoder'(n-1) to  $\vec{y}_L$  and to  $\vec{y}_R$ .

**Problem:** if  $\vec{y}_L = 0^{2^{n-1}}$ , then output of ENCODER'(n-1) is arbitrary, and design can't be correct...  $\Rightarrow$  Must specify output for an all-zeros input.

# **Define** $encoder_n(0^{2^n})$

We augment the definition of the ENCODER<sub>n</sub> function so that its range also includes the all zeros string  $0^{2^n}$ . We define

$$\mathsf{encoder}_n(0^{2^n}) \stackrel{\scriptscriptstyle riangle}{=} 0^n.$$

Note: In ENCODER'(1):  $x[0] \leftarrow y[1]$ , so if input is 00 then output is 0. Hence, ENCODER'(1) also meets this new condition, and the induction basis of the correctness proof holds.

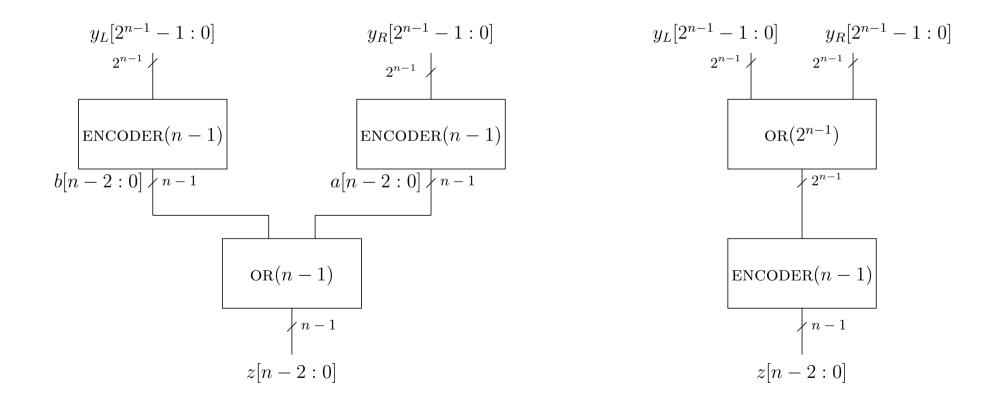

ENCODER'(n) - recursive step

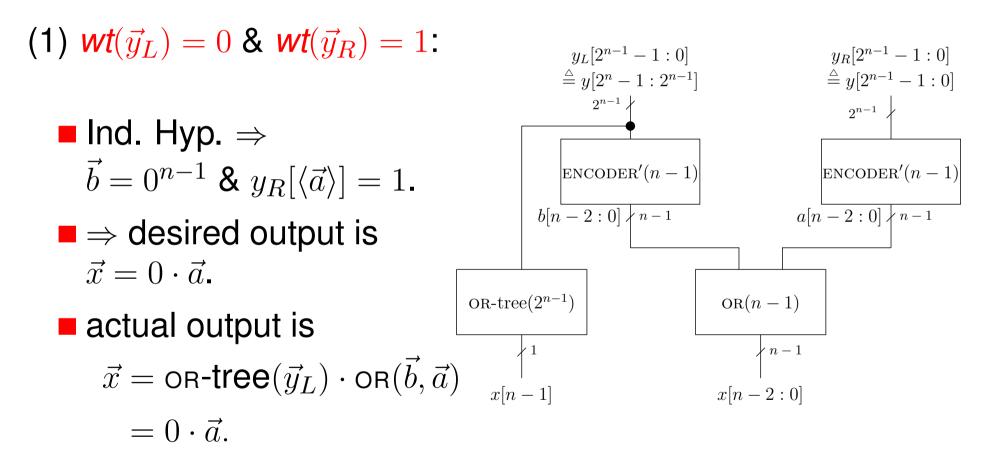

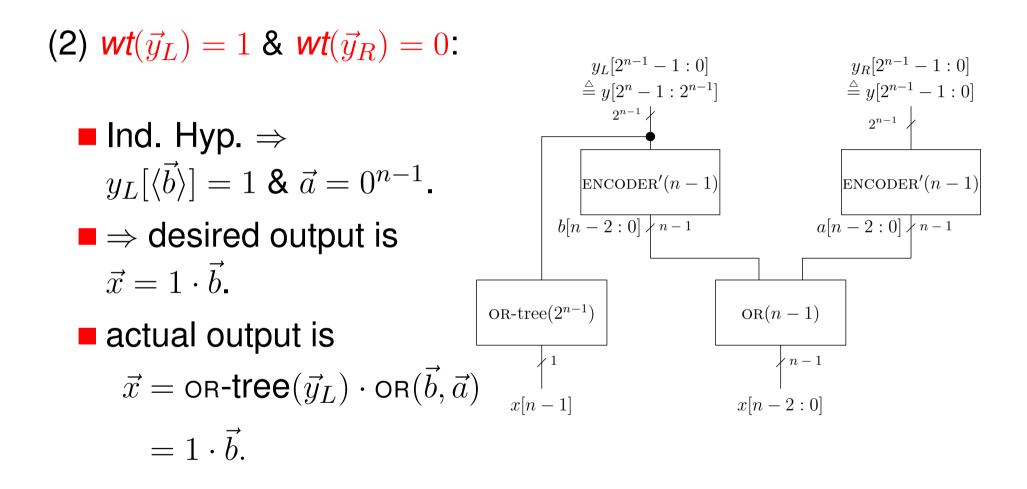

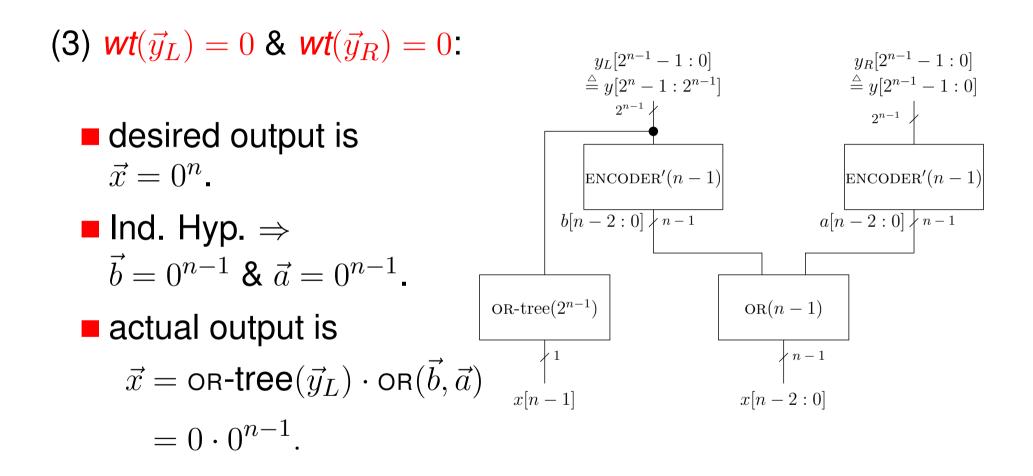

#### Correctness of $\operatorname{encoder}'(n)$ - induction step

Three cases, depending on which "half" of  $\vec{y}$  contains a 1.

#### **Correctness of** ENCODER'(n) - induction step - cont.

#### Correctness of encoder'(n) - induction step - cont.

# Delay analysis of $\mathsf{ENCODER}'(n)$

Let d(n) denote  $t_{pd}(\text{encoder}'(n))$ .

$$d(n) = \begin{cases} 0 & \text{if } n=1\\ \max\{(n-1) \cdot t_{pd}(\mathsf{OR}), d(n-1) + t_{pd}(\mathsf{OR})\} & \text{otherwise.} \end{cases}$$

Guess the solution:  $d(n) = (n-1) \cdot t_{pd}(OR)$ .

# Cost analysis of $\mathsf{ENCODER}'(n)$

Let c(n) denote c(encoder'(n)).

$$c(n) = \begin{cases} 0 & \text{if } n=1\\ 2 \cdot c(n-1) + (2^{n-1}-1+n-1) \cdot c(\text{OR}) & \text{otherwise.} \end{cases}$$

Substitute  $C(2^n) = c(n)$ , and re-write for  $N = 2^n$ :

$$C(N) = 2 \cdot C(N/2) + \Theta(N).$$

$$\Rightarrow \quad C(N) = \Theta(N \log N)$$

$$\Rightarrow \quad c(\operatorname{encoder}'(n)) = \Theta(n \cdot 2^n).$$

# Sanity test

$d(\text{ENCODER}'(n)) = \Theta(n) \& c(\text{ENCODER}'(n)) = \Theta(n \cdot 2^n).$ But we can compute each x[i] using a separate or-tree:

$$x[i] = OR(\{y[j] : bin_n(j)[i] = 1\}).$$

Cost of each tree is  $O(2^n)$  and delay is O(n).

$\Rightarrow$  a trivial design with delay O(n) and cost  $O(n \cdot 2^n)$ .

We conclude that encoder'(n) is not a good design... Can we fix it?!

## Commuting bitwise-OR and ENCODER $_{n-1}$

claim: If  $wt(y[2^n - 1:0]) \le 1$ , then

$\mathrm{Or}(\mathrm{encoder}_{n-1}(\vec{y}_L), \mathrm{encoder}_{n-1}(\vec{y}_R)) = \mathrm{encoder}_{n-1}(\mathrm{Or}(\vec{y}_L, \vec{y}_R)).$

**Proof:** OR $(E_{n-1}(\vec{y}_L), E_{n-1}(\vec{y}_R)) = E_{n-1}(OR(\vec{y}_L, \vec{y}_R))$ Trivial:  $\vec{y} = 0^{2^n}$ .  $wt(\vec{y}_L) = 0 \& wt(\vec{y}_R) = 1$ : Assume that  $y_R[i] = 1$ .  $\Rightarrow$

$$E_{n-1}(\operatorname{OR}(\vec{y}_L, \vec{y}_R)) = E_{n-1}(\operatorname{OR}(0^{2^{n-1}}, \vec{y}_R))$$

$$= E_{n-1}(\vec{y}_R).$$

However,

$$OR(E_{n-1}(\vec{y}_L), E_{n-1}(\vec{y}_R)) = OR(E_{n-1}(0^{2^{n-1}}), E_{n-1}(\vec{y}_R))$$

$$= OR(0^{n-1}, E_{n-1}(\vec{y}_R))$$

$$= E_{n-1}(\vec{y}_R),$$

(other case is analogous) QED

# Correctness of $\operatorname{encoder}^*(n)$

- No need to prove from "the beginning" (although not a hard task).

- Claim proves that  $encoder'(n) \equiv encoder^*(n)$ .

- We already proved that encoder'(n) is correct.

- $\blacksquare \Rightarrow \texttt{encoder}^*(n) \text{ is correct!}$

- Very useful method for hardware design:

- start with a naive design (e.g. naive divide & conquer)

- manipulate design (improve but preserve functionality)

# Cost analysis of $\mathsf{ENCODER}^*(n)$

$$c(\texttt{encoder}^*(n)) = \begin{cases} 0 & \text{if } n=1\\ c(\texttt{encoder}^*(n-1)) + 2^n \cdot c(\texttt{or}) & \text{otherwise.} \end{cases}$$

We expand this recurrence to obtain:

$$\begin{aligned} c(\operatorname{encoder}^*(n)) &= c(\operatorname{encoder}^*(n-1)) + 2^n \cdot c(\operatorname{or}) \\ &= (2^n + 2^{n-1} + \ldots + 4) \cdot c(\operatorname{or}) \\ &= (2 \cdot 2^n - 3) \cdot c(\operatorname{or})) \\ &= \Theta(2^n). \end{aligned}$$

# Delay analysis of $\operatorname{encoder}^*(n)$

The delay of  $encoder^*(n)$  satisfies the following recurrence equation:

$$d(\texttt{encoder}^*(n)) = \begin{cases} 0 & \text{if n=1} \\ \max\{d(\texttt{or-tree}(2^{n-1}), \\ d(\texttt{encoder}^*(n-1) + d(\texttt{or}))\} & \text{otherwise.} \end{cases}$$

Since  $d(\text{OR-tree}(2^{n-1}) = (n-1) \cdot d(\text{OR})$ , it follows that

$$d(\operatorname{encoder}^*(n)) = (n-1) \cdot d(\operatorname{or}) = \Theta(n).$$

Optimality: Prove that the cost and delay of  $encoder^*(n)$  are asymptotically optimal.

# **Summary**

vector notation for schematics and binary strings.

- review of binary representation.

- Decoder & Encoder design, correctness, optimality.

- Techniques:

- Divide & Conquer

- Extend specification to make problem easier

- Evolution improve naive and correct design while preserving functionality.

# Chapter 5: Selectors and Shifters Computer Structure - Spring 2007

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary questions**

- Which types of shifts are you familiar with in your favorite programming language? What is the differences between these shifts? Why do we need different types of shifts?

- How are these shifts executed in a microprocessor?

- Should shifters be considered to be combinational circuits? After all, they simply "move bits around" and do not compute "new bits".

# Goals

#### Selectors:

review definition of multiplexer.

**build** (n:1)-multiplexers.

Shifters:

- Cyclic shifter (Barrel shifter)

- Logical Shifter

- Arithmetic Shifter

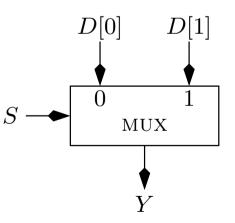

# Multiplexer

**DEF:** A mux-gate (also known as a (2:1)-multiplexer) is a combinational gate that has three inputs D[0], D[1], S and one output Y. The functionality is defined by

$$Y = \begin{cases} D[0] & \text{if } S = 0\\ D[1] & \text{if } S = 1. \end{cases}$$

Equivalently: Y = D[S]

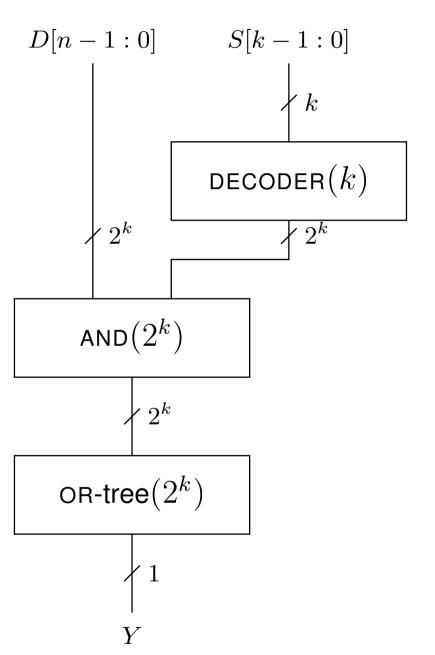

## **Selectors**

**DEF**: An (n:1)-MUX is a combinational circuit defined as follows:

Input: D[n - 1 : 0] and S[k - 1 : 0] where  $k = \lceil \log_2 n \rceil$ . Output:  $Y \in \{0, 1\}$ .

**Functionality:**

$$Y = D[\langle \vec{S} \rangle].$$

**Example:** Let n = 4, D[3:0] = 0101, and S[1:0] = 11. The output Y should be 0.

- **\blacksquare**  $\vec{D}$  data input

- **\blacksquare**  $\vec{S}$  select input

• simplify: assume that n is a power of 2, namely,  $n = 2^k$ .

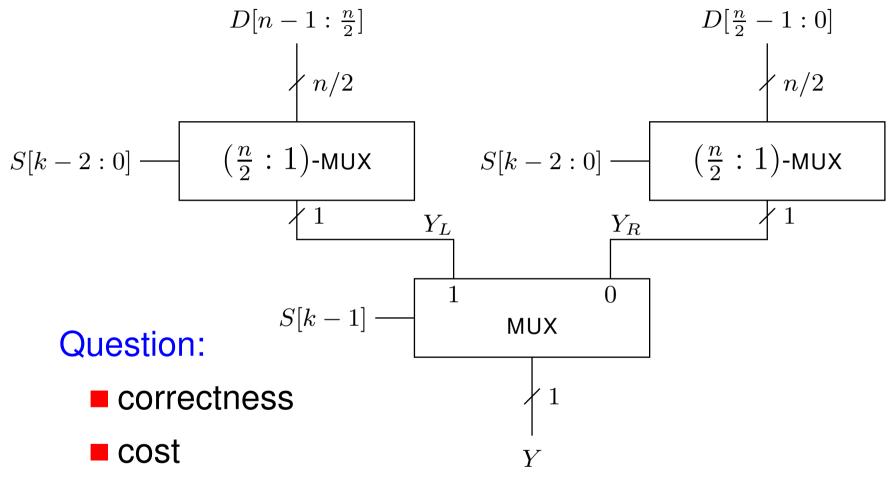

# **Implementation of (n:1)**-MUX

We will present two implementations:

- a decoder based implementation

- a tree-like implementation

#### (n:1)-MUX : a decoder based implementation

# Question:

- correctness

- cost

- delay

- asymptotic optimality

#### (n:1)-MUX : a tree-like implementation

delay

asymptotic optimality

# Which design is better?

both designs are asymptotically optimal.

- based on the tables of Müller & Paul, the tree-like design is better.

- decision is based on specific gate costs in the technology one uses.

- fast MUX-gates in CMOS (transmission gates) do not restore the signals well.

$\Rightarrow$  long paths consisting only of  $\ensuremath{\mathsf{MUX}}\xspace$  are not allowed.

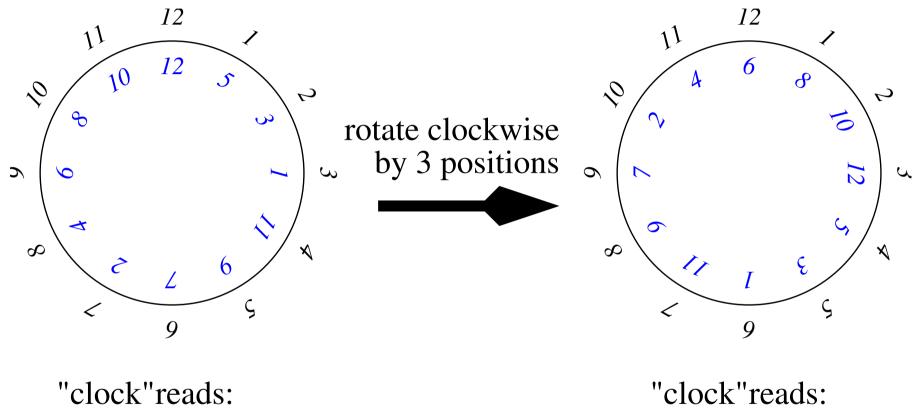

## **Cyclic shift - example**

5,3,1,11,...,8,10,12

"clock"reads: 8,10,12,...,2,4,6

## **Cyclic shift - definition**

The string b[n-1:0] is a cyclic left shift by *i* positions of the string a[n-1:0] if

$$\forall j: \quad b[j] = a[\operatorname{mod}(j-i,n)].$$

**Example:** Let a[3:0] = 0010. A cyclic left shift by one position of  $\vec{a}$  is the string 0100. A cyclic left shift by 3 positions of  $\vec{a}$  is the string 0001.

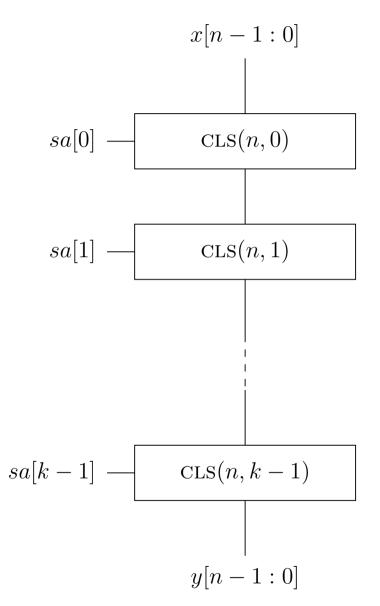

## **Barrel Shifter**

**DEF**: A BARREL-SHIFTER(n) is a combinational circuit defined as follows:

- Input: x[n 1:0] and sa[k 1:0] where  $k = \lceil \log_2 n \rceil$ . Output: y[n - 1:0].

- Functionality:  $\vec{y}$  is a cyclic left shift of  $\vec{x}$  by  $\langle \vec{sa} \rangle$  positions. Formally,

$$\forall j \in [n-1:0]: \ y[j] = x[\operatorname{mod}(j - \langle \vec{sa} \rangle, n)].$$

**\vec{x} - data input**

**\blacksquare**  $\vec{sa}$  - shift amount input

• simplify - assume that n is a power of 2, namely,  $n = 2^k$ .

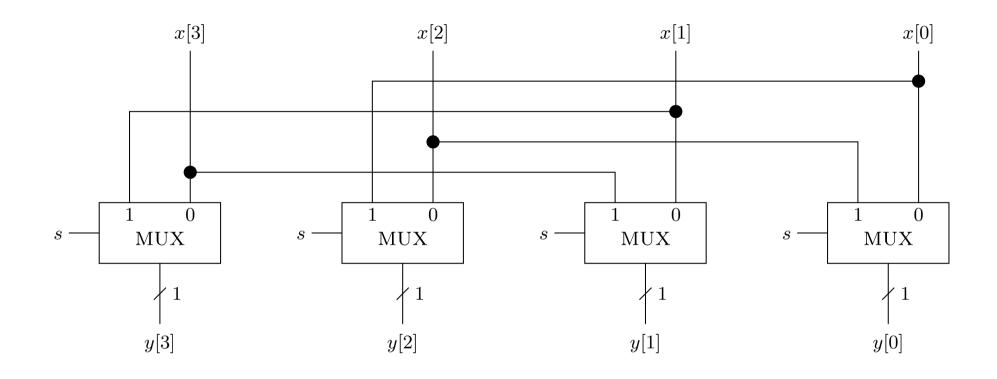

#### CLS(n,i) - Cyclic Left Shift by $2^i$ positions

**DEF**: A CLS(n, i) is a combinational circuit defined as follows:

Input: x[n-1:0] and  $s \in \{0,1\}$ .

**Output:** y[n - 1:0].

**Functionality:**

$$\forall j \in [n-1:0]: y[j] = x[mod(j-s \cdot 2^i, n)].$$

Equivalently,

$$y[j] = \begin{cases} x[j] & \text{if } s = 0\\ x[\operatorname{mod}(j - 2^i, n)] & \text{if } s = 1. \end{cases}$$

$\Rightarrow$  can implement cls(n,i) with a row of n mux-gates.

CLS(4, 1)

Evident that a CLS(n, i) requires a lot of area for the wires. Our model does not capture routing cost.  $\mathsf{barrel-shifter}(n)$  - a chain of  $\mathsf{cls}(n,i)$

### BARREL-SHIFTER(n) - correctness

Define the strings  $y_i[n-1:0]$ , for  $0 \le i \le k-1$ , recursively as follows:

$$y_0[n-1:0] \leftarrow \mathsf{CLS}_{n,0}(x[n-1,0],sa[0])$$

$$y_{i+1}[n-1:0] \leftarrow \mathsf{CLS}_{n,i+1}(y_i[n-1,0],sa[i+1])$$

Claim:  $y_{k-1}[n-1:0]$  is a cyclic left shift of x[n-1:0] by  $\langle sa[k-1:0] \rangle$  positions.

**Proof:** Induction. k = 0 - trivial because cls(n, 0) shifts by zero/one position.

# induction step

$$y_i[j] = \operatorname{cls}_{n,i}(y_{i-1}[n-1,0], sa[i])[j] \quad \text{(by definition of } y_i)$$

=  $y_{i-1}[\operatorname{mod}(j-2^i \cdot sa[i],n)] \quad \text{(by definition of } \operatorname{cls}_{n,i}).$

= Let  $\ell = \operatorname{mod}(j-2^i \cdot sa[i],n).$

= Ind. Hyp.  $\Rightarrow y_{i-1}[\ell] = x[\operatorname{mod}(\ell - \langle sa[i-1:0] \rangle, n).$

= Note that

$$\begin{aligned} \mathsf{mod}(\ell - \langle sa[i-1:0]\rangle, n) &= \mathsf{mod}(j - 2^i \cdot sa[i] - \langle sa[i-1:0]\rangle, n) \\ &= \mathsf{mod}(j - \langle sa[i:0]\rangle, n). \end{aligned}$$

Therefore  $y_i[j] = x[mod(j - \langle sa[i:0] \rangle, n)]$ , and the claim follows.

# **Logical Shifting - motivation**

- Used for shifting binary strings that represent unsigned integers in binary representation.

- Shifting to the left by *s* positions corresponds to

$\langle \vec{y} \rangle \leftarrow \operatorname{mod}(\langle \vec{x} \rangle \cdot 2^s, 2^n).$

Shifting to the right by *s* positions corresponds to

$$\langle \vec{y} \rangle \leftarrow \left\lfloor \frac{\langle \vec{x} \rangle}{2^s} \right\rfloor.$$

#### **Bi-Directional Logical Shifter - definition**

A LOG-SHIFT(n) is a combinational circuit defined as follows:

Input:

•

$$x[n-1:0] \in \{0,1\}^n$$

,

•  $sa[k-1:0] \in \{0,1\}^k$ , where  $k = \lceil \log_2 n \rceil$ , and

•  $\ell \in \{0,1\}$ .

**Output:**  $y[n-1:0] \in \{0,1\}^n$ .

**Functionality:** If  $\ell = 1$ , then logical left shift as follows:

$$y[n-1:0] \stackrel{\scriptscriptstyle riangle}{=} x[n-1-\langle \vec{sa} \rangle:0] \cdot 0^{\langle \vec{sa} \rangle}$$

If  $\ell = 0$ , then logical right shift as follows:

$$y[n-1:0] \stackrel{\scriptscriptstyle \triangle}{=} 0^{\langle \vec{sa} \rangle} \cdot x[n-1:\langle \vec{sa} \rangle].$$

#### **Bi-Directional Logical Shifter - example**

**Example:** Let x[3:0] = 0010. If sa[1:0] = 10 and  $\ell = 1$ , then LOG-SHIFT(4) outputs y[3:0] = 1000. If  $\ell = 0$ , then the output equals y[3:0] = 0000.

#### **Bi-Directional Logical Shifter - implementation**

- As in the case of cyclic shifters, we break the task of designing a logical shifter into sub-tasks of logical shifts by powers of two.

- Loosely speaking, an LBS(n, i) is a logical bi-directional shifter that outputs one of three possible strings:

- the input shifted to the left by  $2^i$  positions,

- the input shifted to the right by  $2^i$  positions, or

- the input without shifting.

We now formally define this circuit....

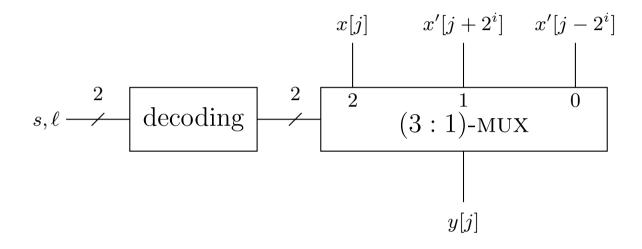

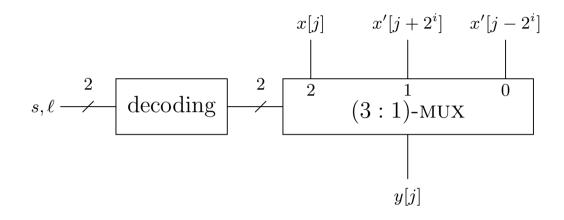

LBS(n, i) - definition

**DEF**: An LBS(n, i) is a combinational circuit defined as follows:

- Input: x[n-1:0] and  $s, \ell \in \{0,1\}$ . Output: y[n-1:0].

- Functionality: Define  $x'[n-1+2^i:-2^i] \in \{0,1\}^{n+2\cdot 2^i}$  as follows:

$$x'[j] \triangleq \begin{cases} x[j] & \text{if } n > j \ge 0 \\ 0 & \text{otherwise.} \end{cases}$$

The value of the output y[n-1:0] is specified by

$$\forall j \in [n-1:0]: y[j] = x'[j+(-1)^{\ell} \cdot s \cdot 2^i].$$

### $y[j] = x'[j + (-1)^\ell \cdot s \cdot 2^i]$

$$x'[n-1+2^i:-2^i] = 0^{2^i} \cdot x[n-1:0] \cdot 0^{2^i}.$$

- $\ell$  determines if the shift is a left shift or a right shift. If  $\ell = 1$  then  $(-1)^{\ell} = -1$ , and the shift is a left shift (since increasing indexes from  $j 2^i$  to j has the effect of a left shift).

- *s* determines if a shift (in either direction) takes place at all. If s = 0, then y[j] = x[j], and no shift takes place.

#### A bit-slice of an implementation of $\mbox{\tiny LBS}(n,i)$

- 1. (3:1)-MUX. Implemented either by a "pruned" tree-like construction or we can simply consider a (3:1)-MUX as a basic gate. Simple circuit  $\Rightarrow$  best option can be easily determined based on the technology at hand.

- 2. decoding circuit not a decoder! Decoding of s and  $\ell$  causes the (3:1)-MUX to select the correct input.

#### A bit-slice of an implementation of $\mbox{\tiny LBS}(n,i)$

Question: This question deals with various aspects and details concerning the design of a logical shifter.

- 1. Design a "pruned" tree-like (3:1)-MUX.

- 2. Design the decoding box.

- 3. Show how LBS(n, i) circuits can be cascaded to obtain a LOG-SHIFT(n). Hint: follow the design of a BARREL-SHIFTER(n).

### **Arithmetic Shifters - motivation**

- Used for shifting binary strings that represent signed integers in two's complement representation.

- Iogical left shifting = arithmetic left shifting.

- Arithmetic right shifting corresponds to dividing by a power of 2 (with sign extension).

#### **Arithmetic right shifter - definition**

**DEF:** An ARITH-SHIFT(n) is a combinational circuit defined as follows:

- Input:  $x[n-1:0] \in \{0,1\}^n$  and  $sa[k-1:0] \in \{0,1\}^k$ , where  $k = \lceil \log_2 n \rceil$ .

- **Output:**  $y[n-1:0] \in \{0,1\}^n$ .

- **Functionality:** The output  $\vec{y}$  is a (sign-extended) arithmetic right shift of  $\vec{x}$  by  $\langle \vec{sa} \rangle$  positions. Formally,

$$y[n-1:0] \stackrel{\scriptscriptstyle \triangle}{=} x[n-1]^{\langle \vec{sa} \rangle} \cdot x[n-1:\langle \vec{sa} \rangle].$$

**Example:** Let x[3:0] = 1001. If sa[1:0] = 10, then ARITH-SHIFT(4) OUTPUTS y[3:0] = 1110.

#### **Arithmetic right shifter - implementation**

Question: Consider the definitions of CLS(n,i) and LBS(n,i). Suggest an analogous definition ARS(n,i) for arithmetic right shift (i.e., modify the definition of  $\vec{x}'$  and use (2:1)-MUXS). Suggest an implementation of an arithmetic right shifter based on cascading ARS(n.i) circuits.

#### **Further questions**

Question: Design a bi-directional cyclic shifter. Such a shifter is like a cyclic left shifter but has an additional input  $\ell \in \{0, 1\}$  that indicates the direction of the required shift. Hint: Consider reducing a cyclic right shift to a cyclic left shifter. To simplify the reduction you may assume that  $n = 2^k - 1$  (hint: use one's complement negation). Suggest a simple reduction in case  $n = 2^k$  (hint: avoid explicit subtraction!).

#### **Further questions - cont.**

Question: CPUs often support all three types of shifting: cyclic, logical, and arithmetic shifting.

- 1. Write a complete specification of a shifter that can perform all three types of shifts.

- 2. Propose an implementation of such a shifter.

# Summary

• (n:1)-multiplexers:

definition.

- two implementations: decoder based & tree-like.

- both designs are optimal.

- three types of shifts: cyclic, logical, and arithmetic shifts.

- Design method: cascade a logarithmic number of shifters (with parameter i) that either perform a shift by 2<sup>i</sup> positions or no shift at all.

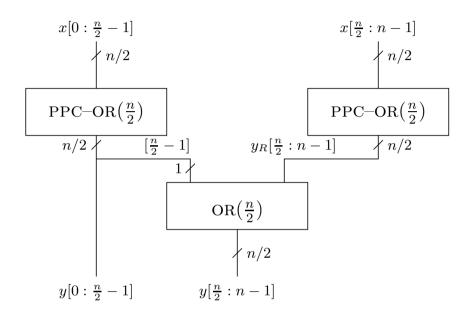

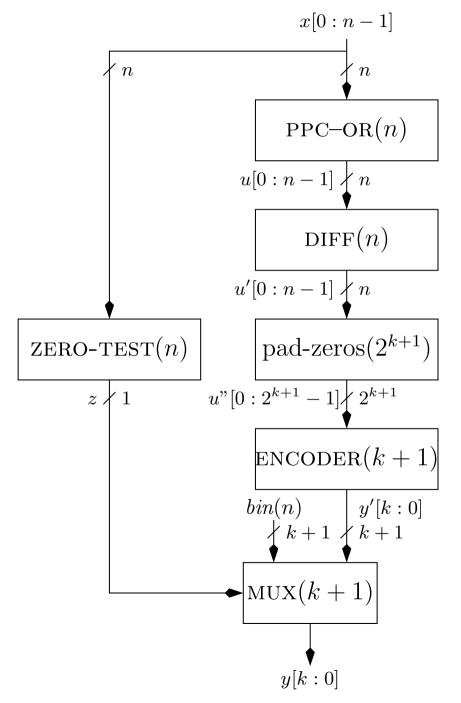

### **Chapter 6: Priority Encoders** *Computer Structure - Spring 2007*

©Dr. Guy Even

Tel-Aviv Univ.

# **Preliminary questions**

- Suppose that many devices wish to transmit data along a shared bus. How does the bus controller decide which device gets to use the bus?

- Consider the binary fraction 0.000010101. In many cases, an arithmetic unit is supposed to shift the fraction so that its value is in the range [1/2, 1) (this is often called *normalization*). How is the shift amount computed?

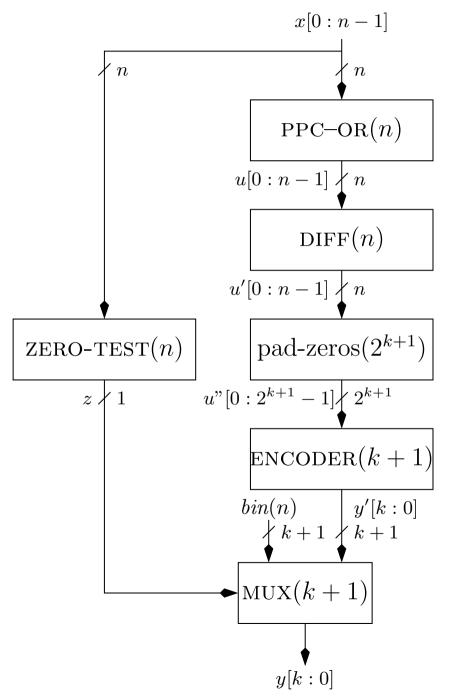

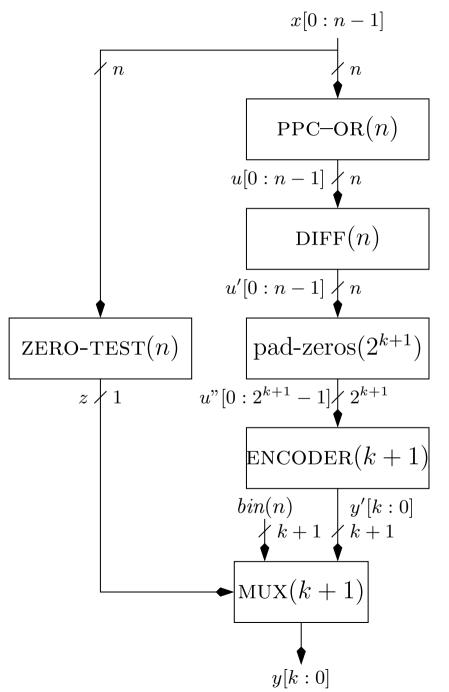

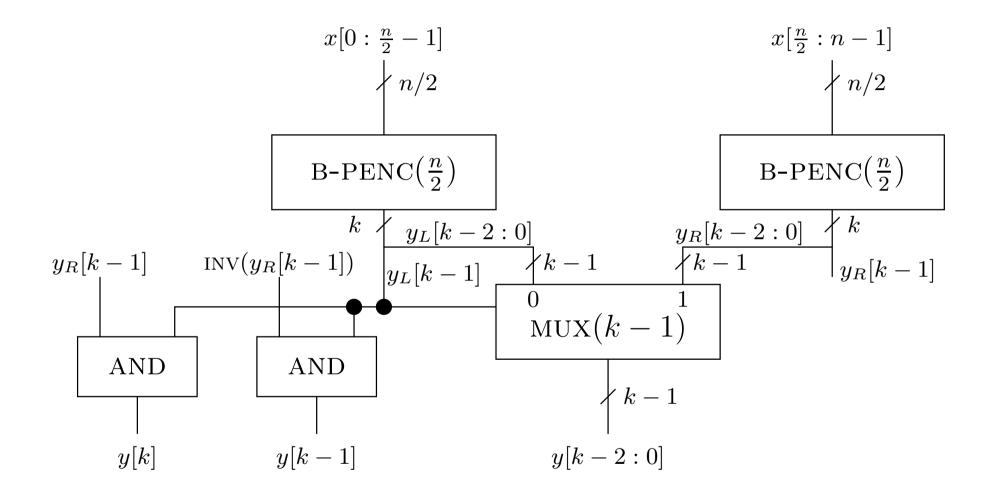

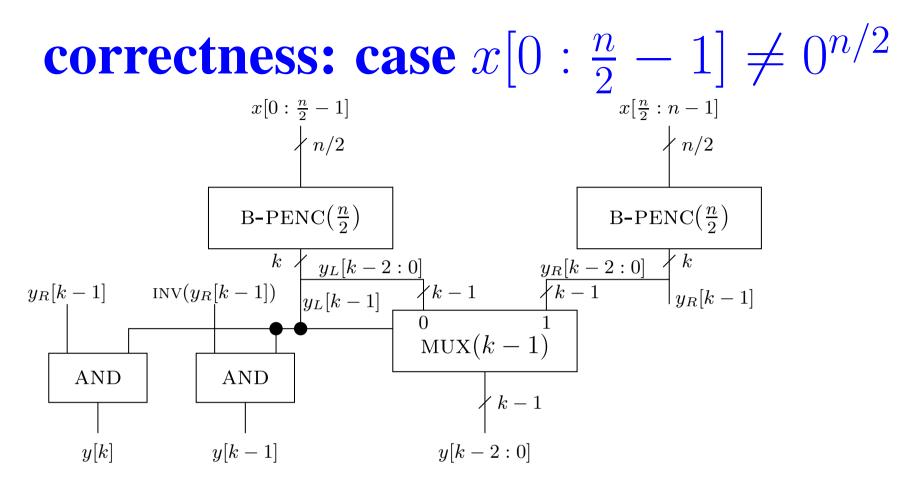

# Leading One