### Digital Logic Design: a rigorous approach © Chapter 10: The Digital Abstraction

Guy Even Moti Medina

School of Electrical Engineering Tel-Aviv Univ.

April 21, 2020

Book Homepage: http://www.eng.tau.ac.il/~guy/Even-Medina

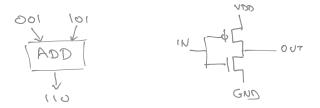

- Can you justify or explain the saying that "computers use only zeros and ones"?

- Can you explain the following anomaly? The design of an adder is a simple task. However, the design and analysis of a single electronic device (e.g., a single gate) is a complex task.

| Property    | Digital Circuit | Analog Device        |

|-------------|-----------------|----------------------|

| values      | $\{0,1\}$       | $\mathbb{R}$         |

| description | simple (Boolean | complicated (differ- |

|             | function)       | ential eq.)          |

| real?       | abstract model  | very real            |

Conclusion: much easier to use the digital abstraction than the realistic, complete, complicated analog model.

- what is an analog device? (components, behavior)

- in what way does a digital circuit model an analog device?

- can every analog device be modeled as a digital circuit?

- what type of digital circuits do we want?

- compare invertes: what makes one inverter better than another?

- how can we tell if an analog device is a gate (say, an inverter)?

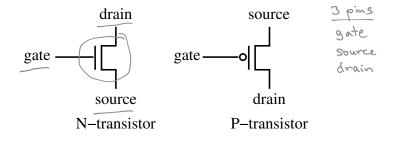

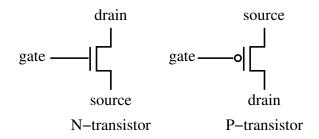

Computers ← VLSI chips ← gates & flip-flops ← transistors Transistors are the basic components. Most common VLSI technology is called CMOS. In CMOS: only two types of transistors:

- N-transistor

- P-transistor

in case you are curious:

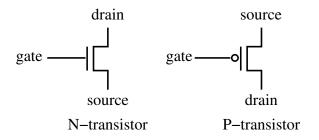

### N-transistor & P-transistor

Inputs: gate & source Output: drain

physically the source and the drain are symmetric, but it is useful to view the source as an input and the drain as an output.

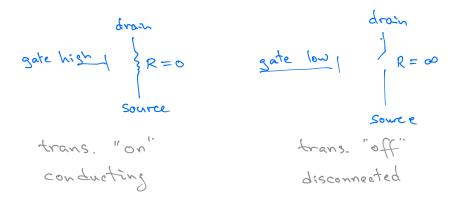

### Functionality of N-transistor:

- If v(gate) = high, then resistance(source, drain) = 0 (and then v(drain) ← v(source))

- If v(gate) = low, then  $resistance(source, drain) = \infty$

Story true if v(source) = low in N. then s.

N-trans.

### Functionality of P-transistor:

- If v(gate) = high, then resistance(source, drain) =  $\infty$

- If v(gate) = low, then resistance(source, drain) = 0

Story true if v(source) = high in P.- trans.

- $V_g$  the voltage of the gate of a transistor.

- *R<sub>sd</sub>* the resistance between the source and a drain of a transistor.

- R<sup>N</sup><sub>sd</sub>(V<sub>g</sub>) the resistance R<sub>sd</sub> in an N-type transistor as a function of the voltage V<sub>g</sub>.

- $R_{sd}^{P}(V_g)$  same in a P-type transistor.

- $V_{low} < V_{high}$  two threshold voltages (the values of  $V_{low}$  and  $V_{high}$  depend on the technology).

$$R_{sd}^{N}(V_{g}) \stackrel{\scriptscriptstyle \triangle}{=} \begin{cases} \infty & \text{if } V_{g} < V_{low} \\ 0 & \text{if } V_{g} > V_{high} \end{cases}$$

$$R_{sd}^{P}(V_{g}) \stackrel{\scriptscriptstyle \triangle}{=} \begin{cases} 0 & \text{if } V_{g} < V_{low} \\ \infty & \text{if } V_{g} > V_{high} \end{cases}$$

In reality, zero resistance means a very small resistance, and infinite resistance means a very high resistance.

- The voltages in an electronic circuit change when the circuit is engaged in some computation.

- We distinguish between the changes (or transitions) that are supposed to be very fast, and the periods between transitions that are called the steady state.

Example: two players X and Y are passing a ball to each other. We regard the travel from one player to the other as a transition. We regard the state of the ball as steady if the ball is held by one of the players. Thus, we say that the ball alternates between the states X and Y. N-type transistor:

- If V<sub>g</sub> > V<sub>high</sub>, then R<sup>N</sup><sub>sd</sub> = 0. voltage of drain = voltage of source.

- If  $V_g < V_{low}$ , then  $R_{sd}^N = \infty$ . So, voltage of the drain is unchanged by the transistor.

- A P-type transistor behaves in a dual manner:

• If

$$V_g > V_{high}$$

, then  $R_{sd}^N = \infty$ .

• If

$$V_g < V_{low}$$

, then  $R_{sd}^N = 0$ .

### Nonlinear behavior of transistors

Note that this description of transistor behavior implies that transistors are highly non-linear. (Recall that a linear function f(x) satisfies  $f(a \cdot x) = a \cdot f(x)$ .)

Figure:  $R_{sd}$  as a function of  $V_g$ .

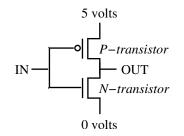

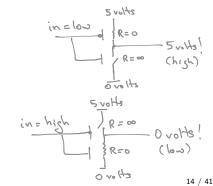

### Example: a CMOS inverter

### If IN = low, then:

- P-transistor is conducting

- N-transistor is not conducting

$\Rightarrow v(OUT) = high$ If IN = high, then:

- P-transistor is not conducting

- N-transistor is conducting

$$\Rightarrow v(OUT) = low$$

Qualitative analysis:

- gives an idea about "how an inverter works".

- no idea about actual voltages of output as a function input voltage.

- ${\ensuremath{\bullet}}$  no idea about how long it takes the output to stabilize.

Quantitative analysis:

- based on precise modeling of transistor.

- computes precise input-output relationship.

- requires a lot of work (usually done with the aid of a computer program called SPICE).

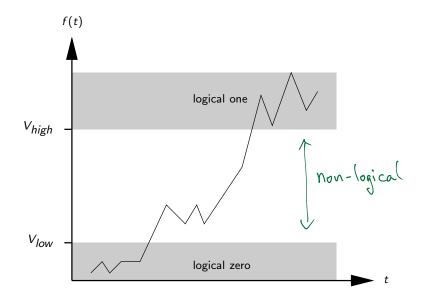

An analog signal is a real function

time voltage

$$f: \mathbb{R} \to \mathbb{R},$$

where f(t) = voltage as a function of the time.

Assumption: wires have zero resistance, zero capacity, and signals propagate through wires without delay.

$\Rightarrow$  voltage along a wire is identical at all times.

Since a signal describes the voltage (i.e. derivative of energy as a function of charge), we also assume that a signal is a continuous function.

f(k) = q

### A digital signal is a function لزيمو

$$g:\mathbb{R}\to \{0,1,\text{non-logical}\}.$$

The value of a digital signal describes the logical value carried along a wire as a function of time.

- zero & one : logical values.

- non-logical: indicates that the signal is neither zero or one.

Q: How does one interpret an analog signal as a digital signal? naive answer: define a threshold voltage V'. Given an analog signal f(t), the digital signal dig(f(t)) is defined as follows.

$$\mathit{dig}(f(t)) \stackrel{\scriptscriptstyle riangle}{=} egin{cases} 0 & ext{if } f(t) < V' \ 1 & ext{if } f(t) > V' \end{cases}$$

Q: is this a useful definition?

## problems with definition of dig(f(t))

- All devices in a circuit must use exactly the same threshold V'. This is impossible due to manufacturing tolerances.

- Perturbations of f(t) around the threshold V' lead to unexpected values of dig(f(t)).

#### Example

Measure weight w by measuring the length  $\ell$  of a spring. Suppose we wish to know if w > w'. This can be done by checking if  $\ell > \ell'$ . However, spring length oscillates around  $\ell$ . If  $\ell \approx \ell'$ , then comparison requires a long time.

$\Rightarrow$  must use separate thresholds for 0 and for 1.

Q: How does one interpret an analog signal as a digital signal? A: Two voltage thresholds are defined:  $V_{low} < V_{high}$ . Given an analog signal f(t), The digital signal dig(f(t)) is defined as follows.

$$dig(f(t)) \triangleq \begin{cases} 0 & \text{if } f(t) < V_{low} \\ 1 & \text{if } f(t) > V_{high} \\ \text{non-logical otherwise.} \end{cases}$$

### digital interpretation of an analog signal

- manufacturing requirements:

- a low output must be  $\leq V_{low}$  & a high output must be  $\geq V_{high}$ .

- fluctuations of f(t) around  $V_{low}$  still cause fluctuations of dig(f(t)).

However, these fluctuations are between 0 and "non-logical" (not between 0 and 1). This is still a problem, but not as bad...

# Q: define an inverter. A: $dig(OUT(t)) \stackrel{\triangle}{=} \begin{cases} 0 & \text{if } dig(IN(t)) = 1 \\ 1 & \text{if } dig(IN(t)) = 0 \\ arbitrary & \text{otherwise.} \end{cases}$

We will see shortly that noise makes this definition useless. But, first introduce new players: transfer functions and noise...

### Definition

transfer function - the relation between the voltage at an output of a gate and the voltages of the inputs of the gate.

#### Example

An inverter with an input x and an output y. The value of the signal y(t') at time t' is a function of the signal x(t) in the interval  $(-\infty, t']$ .

Static transfer function: if the input x(t) is stable for a sufficiently long period of time and equals  $x_0$ , then the output y(t) stabilizes on a value  $y_0$  that is a function of  $x_0$ .  $\Im({}^{t}) = \Im(x_0)$ history vs. present: if a device does not have a static transfer function, then it is not a logical gate. It might be still useful (e.g., memory device or oscillator).

### Static transfer function

### Definition

A function  $f : \mathbb{R} \to \mathbb{R}$  is a static transfer function of a device G if

- $\Delta$  propagation delay (time required for stable output)

- x<sub>0</sub> stable input voltage

- $t_0$  time in which y(t) is measured

#### Definition

A device is a gate if it has a static transfer function.

A gate might not be a logical gate...

(1) Since circuits operate over a bounded range of voltages, static transfer functions are usually only defined over bounded domains and ranges (say [0, 5] volts).

(2) Allow perturbations of

$$x(t)$$

and  $y(t)$ .

$\forall \epsilon \; \exists \delta, \Delta > 0 \; \forall x_0, t_1, t_2 :$

$\forall t \in [t_1, t_2] : \; |x(t) - x_0| \leq \delta$

$\Rightarrow$

$\forall t \in [t_1 + \Delta, t_2] : \; |y(t) - f(x_0)| \leq \epsilon.$

- $\delta$  measures stability of input x(t)

- $\epsilon$  measures stability of output y(t)

- $[t_1, t_2]$  interval during which x(t) is  $\delta$ -stable.

- $[t_1 + \Delta, t_2]$  interval during which y(t) is  $\epsilon$ -stable.

(3) Usually, we restrict our attention to values of  $x_0$  such that  $dig(x_0) \in \{0, 1\}$ .

An inverter is a gate whose static transfer function f satisfies:

$$dig(f(x)) \stackrel{\scriptscriptstyle riangle}{=} \begin{cases} 0 & \text{if } dig(x) = 1\\ 1 & \text{if } dig(x) = 0\\ arbitrary & otherwise. \end{cases}$$

Same method can be used to define other gates (OR,NAND,etc.).

Noise = undesired changes to f(t). Back to the example of a weight hanging from a spring: wind causes changes in the spring length and disturbs measurement of spring length.

$$A(t) \longrightarrow B(t)$$

Noise signal: the difference B(t) - A(t). (reference signal = A(t)).

$$B(t) = A(t) + n_B(t).$$

Q: What causes noise?

A: The main source of noise is heat. Heat causes random movement of electrons. These random movements do not cancel out perfectly, and random currents are created. These random currents create perturbations in the voltage.

- Bounded noise model the noise signal along every wire has a bounded absolute value.

- Uniform bounded noise model:

$\exists \epsilon > 0$  such that : | *noise*  $| \leq \epsilon$ .

• Justification - noise is a random variable whose distribution has a rapidly diminishing tail. If  $\epsilon$  is sufficiently large, then

$Prob[|noise| > \epsilon] \approx 0.$

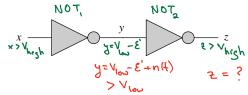

#### The digital abstraction in the presence of noise

Assume that:

•

$$x > V_{high}$$

, so  $dig(x) = 1$ ,

•  $y = V_{low} - \epsilon'$ , for a very small  $\epsilon' > 0$ .

•  $\Rightarrow dig(z) = 1$ .

What if input to 2nd inverter equals  $y(t) + n_y(t)$ ? If  $n_y(t) > \epsilon'$ , then  $dig(y(t) + n_y(t)) =$  non-logical, and can't deduce that dig(z) = 1.

$\Rightarrow$  must strengthen the digital abstraction!

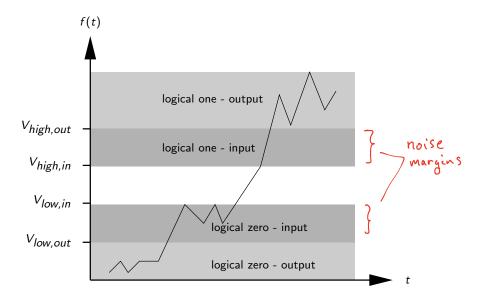

Deal with noise: interpret input signals and output signals differently. Input Signal: a signal measured at an input of a gate. Output Signal: a signal measured at an output of a gate. Instead of two thresholds,  $V_{low}$  and  $V_{high}$ , we define the following four thresholds:

### Redefining the digital interpretation (cont.)

Consider an input signal  $f_{in}(t)$ . The digital signal  $dig(f_{in}(t))$  is defined as follows.

$$dig(f_{in}(t)) \stackrel{\scriptscriptstyle \triangle}{=} \begin{cases} 0 & \text{if } f_{in}(t) < V_{low,in} \\ 1 & \text{if } f_{in}(t) > V_{high,in} \\ \text{non-logical} & \text{otherwise.} \end{cases}$$

Consider an output signal  $f_{out}(t)$ . The digital signal  $dig(f_{out}(t))$  is defined analogously.

$$dig(f_{out}(t)) \stackrel{\scriptscriptstyle riangle}{=} \begin{cases} 0 & ext{if } f_{out}(t) < V_{low,out} \\ 1 & ext{if } f_{out}(t) > V_{high,out} \\ ext{non-logical} & ext{otherwise.} \end{cases}$$

### Noise margins

The following differences are called noise margins.

#### Claim

Suppose that g(t) = f(t) + n(t), where |n(t)| is less than the noise margin. If  $dig(f)(t) \in \{0,1\}$ , then dig(g(t)) = dig(f(t)).

#### Proof.

If

$$dig_{out}(f)(t) = 0$$

, then  $f(t) < V_{low,out}$ . Hence,

$$g(t) = f(t) + n(t)$$

$< V_{low,out} + (V_{low,in} - V_{low,out}) = V_{low,in}.$

Therefore,  $dig_{in}(g)(t) = 0$ , as required. The case  $dig_{out}(f)(t) = 1$  is analogous.

We are now ready to define an inverter.

#### Definition

Let G denote a device with one input x and one output y. The device G is an inverter if its static transfer function f(x) satisfies:

$$\begin{aligned} x(t) < V_{low,in} \Longrightarrow y(t) > V_{high,out} \\ x(t) > V_{high,in} \Longrightarrow y(t) < V_{low,out}. \end{aligned}$$

Distinction between inputs and outputs is applied to other gates as well.

### Logical & stable analog signals

back to the zero-noise model (to simplify the discussion)... logical signal: f(t) is logical at time t if  $dig(f(t)) \in \{0, 1\}$ . stable signal: f(t) is stable during the interval  $[t_1, t_2]$  if f(t) is logical for every  $t \in [t_1, t_2]$ .

#### Claim

If an analog signal f(t) is stable during the interval  $[t_1, t_2]$  then one of the following holds:

$${f 0}$$

dig $(f(t))=0$ , for every  $t\in [t_1,t_2]$ , or

3 dig

$$(f(t)) = 1$$

, for every  $t \in [t_1, t_2]$ .

### Proof.

Continuity of  $f(t) \& V_{low} < V_{high}$ .

Let x(t) denote a digital signal. logical signal: x(t) is logical at time t if  $x(t) \in \{0, 1\}$ . stable signal: x(t) is stable during the interval  $[t_1, t_2]$  if x(t) is logical for every  $t \in [t_1, t_2]$ .

- Signals analog & digital

- Noise bounded noise model & zero noise model

- Digital interpretation of analog signals

- Transfer functions

- Definition of gate (e.g. inverter) using transfer function

- Stable & logical signals