## Digital Logic Design: a rigorous approach © Chapter 21: The ISA of a Simplified DLX

Guy Even Moti Medina

School of Electrical Engineering Tel-Aviv Univ.

June 7, 2020

Book Homepage: http://www.eng.tau.ac.il/~guy/Even-Medina

- According to the Collins Dictionary "architecture" means the art of planning, designing, and constructing buildings.

- Computer architecture refers to computers instead of buildings.

- Computers are complicated.

- Very simple microprocessor is built from tens of thousands of gates and an operating system spans thousands of lines of instructions.

## Why use abstractions? (cont)

- To simplify things, people focus at a given time on certain aspects of computers and ignore other aspects.

- the hardware designer ignores questions such as: which programs will be executed by the computer?

- The programmer, on the other hand, often does not even know exactly which type of computer will be executing the program she is writing.

- The architect is supposed to be aware of different aspects so that the designed system meets the required price and performance goals.

- Several abstractions are used in computer systems.

- We focus on three abstractions used by different "players":

- The C programmer (who writes programs)

- The user (who executes programs)

- The hardware designer.

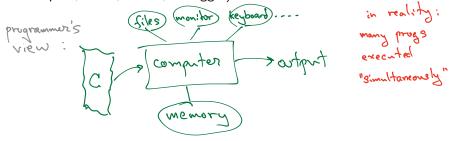

The C programmer uses the abstraction of a computer that runs C programs, owns a private memory, and has access to various peripheral devices (such as a printer, a monitor, a keyboard, etc.). Supporting this abstraction requires software tools (e.g., editor, compiler, linker, loader, debugger).

The user, who runs various applications, uses the abstraction of a computer that is capable of running several applications concurrently, supports a file system, and responds to mouse movements and typing on the keyboard. Supporting the user's abstraction requires an operating system (to coordinate between several programs running in the same time and manage the file system), and hardware (that executes programs, but not in C).

coordination.

ny 05

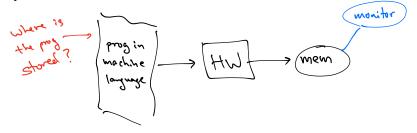

The hardware designer, is given a specification, called the Instruction Set Architecture (in short, ISA). Her goal is to design a circuit that implements this specification while minimizing cost and delay.

### The architect and the ISA

- The architect is supposed to be aware of these different viewpoints.

- The architect's main goal is to suggest an ISA.

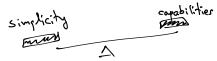

- On one hand, this ISA should provide support for the users of the ISA (these are the programmer, the end user, and even the operating system).

- On the other, the ISA should be simple enough so that the hardware designer can come up with an implementation that is not too expensive or slow.

- What exactly is the ISA?

- The ISA is a specification of the microprocessor from the programmer's point of view.

- However, this is not a C programmer or a programmer that is programming in a high level language. Instead, this is a programmer programming in machine language.

- Since it is not common anymore for people to program in machine language, the machine language programmer is actually a program!

### The Pair: Compiler & Assembler

- Programs in machine language are output by a program called an assembler.

- The input of an assembler is a program in assembly language. Most assembly programs are also written by programs called compilers.

- Compilers are input a program in a high level language and output assembly programs.

- Hence a C program undergoes the following sequence of translations: 1. The compiler translates it to an assembly program. 2. The assembler translates it to a machine language program.

This two-stage sequence of translations starting from a C program and ending with a machine language program has several advantages:

- The microprocessor executes programs written in a very simple language (machine language). This facilitates the design of the microprocessor.

- The C programmer need not think about the actual platform that executes the program.

- Only one compiler is required. For each platform, there is an assembler that translates the assembly programs to the machine language of the platform.

- Every stage of the translation works in a certain abstraction. The amount of detail increases as one descends to lower level abstractions. In each translation step, decisions can be made that are suited to the current abstraction.

who compiles the compiler?

who compiles the assembler?

- The machine language of a processor is often called an instruction set.

- In general, a machine language has very few rules and a very simple syntax. In the case of the simplified DLX, every sequence of instructions constitutes a legal program (is this the case in C or in Java?).

- This explains why the machine language is referred to simply as a set of instructions.

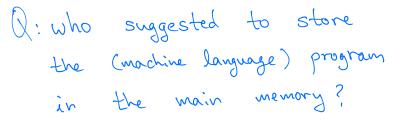

The main memory is used to store both the program itself (i.e., instructions) and the data (i.e., constant and variables used by the program). We regard the memory as an array  $M[0:2^{32}-1]$  of words. Each element M[i] in the array holds one word. The memory is organized like a Random Access Memory (RAM). This means that the processor can access the memory in one of two ways:

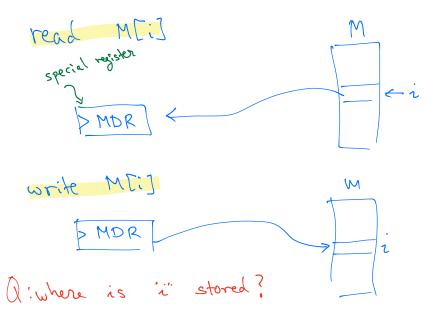

- Read or load *M*[*i*]. Request to copy the contents of *M*[*i*] to a register called *MDR* (Memory Data Register).

- Write or store in *M*[*i*]. Request to store the contents of a register called *MDR* in *M*[*i*].

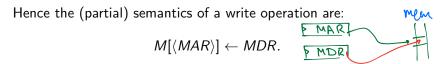

Note the angular brackets around the MAR; they signify that we interpret the binary string stored in the MAR as a binary number. Similarly, the (partial) semantics of a read operation are:

$MDR \leftarrow M[\langle MAR \rangle].$

For example, in a read operation we need to

- compute the address and store it in the MAR,

- copy the contents of the accessed word in the memory to the MDR, and

- Solution contents of the *MDR* to a general purpose register.

However, from the point of view of the memory, the interaction with the microprocessor is via the *MAR* and *MDR*. This relatively neat description is incorrect when we consider the task of reading an instruction from the memory. As we will see later, the address of an instruction is stored in a register called PC and  $M[\langle PC \rangle]$  is stored in a register called IR.

The registers serve as the working space of the microprocessor. They have three main purposes:

- (1) to control the microprocessor (e.g., the PC and IR),

- to serve as the scratch pad for data (e.g., the GPRs), or

- $\odot$  an interface with the main memory (e.g., MAR and MDR).

PC = prog. counter = address of current instruction IR = instruction register = current instruction GPR = general purpose regs (scratchpad) MAR/MDR = interface to main mem. The architectural registers of the simplified DLX are all 32 bits wide and listed below.

- 32 General Purpose Registers (GPRs) indexed from 0 to 31.

We refer to these registers as R0 to R31. Loosely speaking, the general purpose registers are the objects that the program directly manipulates. Register R0 is an exception, as its contents always equals 0<sup>32</sup> and cannot be modified.

- Program Counter (PC). The PC stores the address (i.e., index in memory) of the instruction that is currently being executed.

- Instruction Register (IR). The IR stores the current instruction (i.e.,  $IR = M[\langle PC \rangle]$ ).

- Special Registers: MAR, MDR. As mentioned above, these registers serve as the interface between the microprocessor and the memory when data is written and read.

- Instructions are separated to memory accesses and "computations".

- The arguments and result of computations are stored in GPRs.

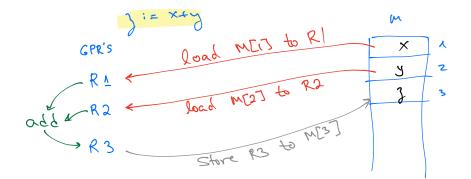

#### Example

Consider a high level instructions z := x + y. Such an instruction is implemented by the following sequence of instructions. Suppose that x is stored in M[1], y is stored in M[2], and z is stored in M[3]. We first need to copy x and y to the GPRs. Namely, we first need to perform two read operations that copy M[1] to R1 and M[2] to R2. We then perform the actual addition: R3  $\leftarrow$  R1 + R2. Finally, we copy R3 using a write operation to the memory location M[3].

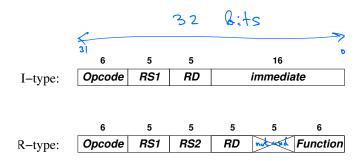

### Instruction Formats

Figure: Instruction formats of the simplified DLX. (Bits are ordered in descending order; namely, the leftmost bit is in position [31] and the rightmost bit is in position [0].)

32 GPRS: RO--- R31.

index of GPR Ri can be represented using 5 bits

$$(2^5 = 32)$$

.

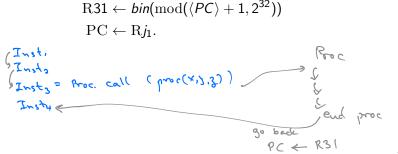

Load and store instructions deal with copying words between the memory and the GPRs. An informal and abbreviated interpretation of the load and store instruction is given in the table below.

| Load/Store    | Semantics                |

|---------------|--------------------------|

|               | RD := M[sext(imm) + RS1] |

| sw RD RS1 imm | M[sext(imm)+RS1] := RD   |

#### Definition

The effective address in a load or store instruction is defined as follows. Let  $j = \langle RS1 \rangle$ , namely the binary number represented by the 5-bit field RS1 in the instruction. Let Rj denote the word stored in the register of the GPR whose index is j. Let  $\langle Rj \rangle$  denote the binary number represented by Rj. Recall that [imm] denotes the two's complement number represented by the 16-bit field *imm*. We denote the effective address by *ea*. Then,

$ea \stackrel{\triangle}{=} \operatorname{mod}(\langle \mathrm{R}j \rangle + [imm], 2^{32}).$

We point out that the event that  $\langle Rj \rangle + [imm] \notin \{0, \ldots, 2^{32} - 1\}$  is (most likely) an indication of a programming error. In certain architectures, such an event creates a segmentation fault. In the simplified DLX, we do not consider this event to be an error, and the modulo operation is a side effect of using a simple adder for computing the effective address

#### Definition

Let  $i = \langle RD \rangle$ , namely *i* is the number represented in binary representation by the 5-bit field RD in the instruction. Let Ri denote the word stored in the *i*th register in the GPR.

$\mathbf{R}i \leftarrow M[ea].$

This means that the word stored in M[ea] is copied to register Ri. Of course, M[ea] retains its value.

A store instruction has the following meaning:

$M[ea] \leftarrow \mathrm{R}i.$

This means that the word stored in  $R_i$  is copied to M[ea]. Of course,  $R_i$  retains its value.

Following the notation used for load and store instructions, we use the following notation:

- Ri denotes the word stored in the register of the GPR whose index is (RD).

- Rj<sub>1</sub> denotes the word stored in the register of the GPR whose index is (RS1).

- R<sub>j2</sub> denotes the word stored in the register of the GPR whose index is (RS2).

There are two add instructions in the ISA. We describe below the add instruction that belongs to the I-type format. In the table below an informal description is provided.

| Instruction     | Semantics             |

|-----------------|-----------------------|

| addi RD RS1 imm | RD := RS1 + sext(imm) |

The precise semantics of an add-immediate instruction are as follows.

$$Ri \leftarrow bin(mod([Rj_1] + [imm], 2^{32})).$$

(1)

$$Ri \leftarrow bin(mod([Rj_1] + [imm], 2^{32})).$$

(1)

$$Ri \leftarrow bin(mod([Rj_1] + [imm], 2^{32})).$$

(1)

The shift instructions perform a logical shift by one position either to the left or to the right. The input is word  $Rj_1$  and the shifted word is stored in Ri.

|       | Instruction  | Semantics      |

|-------|--------------|----------------|

| Seft. |              | RD := RS1 << 1 |

| Why   | 🚽 srl RD RS1 | RD := RS1 >> 1 |

| Instruction    | Semantics           |

|----------------|---------------------|

|                | RD := RS1 + RS2     |

|                | RD := RS1 - RS2     |

| and RD RS1 RS2 | RD := AND(RS1, RS2) |

| or RD RS1 RS2  | RD := OR(RS1, RS2)  |

| xor RD RS1 RS2 | RD := XOR(RS1, RS2) |

Formally, the semantics of the add and subtract instructions are:  $Ri \leftarrow bin(mod([Rj_1] + [Rj_2], 2^{32}))$  $Ri \leftarrow bin(mod([Rj_1] - [Rj_2], 2^{32})).$

The semantics of the bitwise logical instructions are simple. For example, in an AND instruction  $Ri[\ell] = AND(Rj_1[\ell], Rj_2[\ell])$ .

The test instructions compare the two's complement numbers  $[R_{j_1}]$  and [imm]. The result of the comparison is stored in  $R_i$ . For example, consider the slti instruction. The semantics of the slti instruction are:

$$\mathbf{R}i = \begin{cases} 1 & \text{if } [\mathbf{R}j_1] < [imm] \\ 0 & \text{otherwise.} \\ 1 & 0 \end{cases}$$

| Instruction               | Semantics                           |

|---------------------------|-------------------------------------|

| s <i>rel</i> i RD RS1 imm | RD := 1, if condition is satisfied, |

|                           | RD := 0 otherwise                   |

| if <i>rel</i> =1t         | test if $RS1 < sext(imm)$           |

| if <i>rel</i> =eq         | test if $RS1 = sext(imm)$           |

| if <i>rel</i> =gt         | test if RS1 > sext(imm)             |

| if <i>rel</i> =1e         | test if RS1 $\leq$ sext(imm)        |

| if <i>rel</i> =ge         | test if $RS1 \ge sext(imm)$         |

| if <i>rel</i> =ne         | test if RS1 $\neq$ sext(imm)        |

|                           | · · · · ·                           |

(w.r.t. 2's comp repr.)

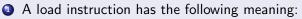

Branch and jump instructions modify the value stored in the the PC. Recall that during the execution of every instruction the PC is incremented. In a branch or jump instruction an additional change is made to the PC.

The simplest instruction in this set is the "jump register" (jr) instruction. It simply changes the PC so that  $PC \leftarrow Rj_I$ . Hence the next instruction to be executed is the instruction stored in

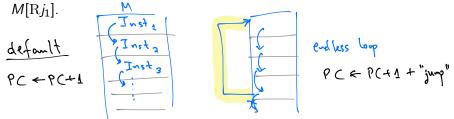

A somewhat more evolved instruction is the "jump and link register" (jalr) instruction. This instruction saves the incremented PC in R31. The idea is that this instruction is used for calling a procedure and the return address is stored in R31. Formally, the semantics of jalr are:

31 / 43

We also have two branch instructions: "branch if zero" (beqz) and "branch if not zero" (bnez). In a beqz instruction,

- if  $Rj_1 = 0^{32}$  then a branch takes place and the address of the next instruction is PC + 1 + [imm].

- If Rj<sub>1</sub> ≠ 0<sup>32</sup>, then the branch is not taken, and the address of the next instruction is PC + 1. In a bnez instruction, the conditions are reversed.

| Instruction  | Semantics                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| beqz RS1 imm | $\begin{array}{l} PC = PC + 1 + sext(imm), \ if \ RS1 = 0 \\ PC = PC + 1, \ if \ RS1 \neq 0 \\ PC = PC + 1, \ if \ RS1 = 0 \\ PC = PC + 1 + sext(imm), \ if \ RS1 \neq 0 \end{array}$ |

|              | $PC = PC + 1$ , if $RS1 \neq 0$                                                                                                                                                       |

| bnez RS1 imm | PC = PC + 1, if $RS1 = 0$                                                                                                                                                             |

|              | $PC = PC + 1 + sext(imm)$ , if $RS1 \neq 0$                                                                                                                                           |

| ir RS1       | PC = RS1                                                                                                                                                                              |

| jalr RS1     | R31 = PC+1; PC = RS1                                                                                                                                                                  |

There are a few special instructions in the I-type format.

- The first special instruction is a the "no operation" (special-nop) instruction. This instruction has a null effect, and the only thing that happens during its execution is that the PC is incremented.

- The second special instruction is the "halt" (halt) instruction. This instruction causes the microprocessor to "freeze" and stop the execution of the program.

# I-type instructions

|                   |                 | • ·                                      |

|-------------------|-----------------|------------------------------------------|

| IR[31 : 26]       | Mnemonic        | Semantics                                |

| Data Transf       | er              |                                          |

| 100 011           | lw              | RD = M[sext(imm) + RS1]                  |

| 101 011           | SW              | $M[sext(imm){+}RS1] = RD$                |

| Arithmetic,       | Logical Operati | on                                       |

| 001 011           | addi            | RD = RS1 + sext(imm)                     |

| Test Set Op       | eration         |                                          |

| 011 rel           | s rel i         | $RD=(RS1 \; rel \; sext(imm))$           |

| 011 001           | sgti            | RD = (RS1 > sext(imm))                   |

| 011 010           | seqi            | RD = (RS1 = sext(imm))                   |

| 011 011           | sgei            | $RD = (RS1 \ge sext(imm))$               |

| 011 100           | slti            | RD = (RS1 < sext(imm))                   |

| 011 101           | snei            | $RD = (RS1 \neq sext(imm))$              |

| 011 110           | slei            | $RD = (RS1 \le sext(imm))$               |

| Control Operation |                 |                                          |

| 000 100           | beqz            | PC = PC + 1 + (RS1 = 0 ? sext(imm))      |

| 000 101           | bnez            | $PC = PC + 1 + (RS1 \neq 0 ? sext(imm))$ |

| 010 110           | i.              | $DC = DC1$ $\frac{35}{43}$               |

| IR[5 : 0]                     | Mnemonic | Semantics         |

|-------------------------------|----------|-------------------|

| Shift Ope                     | ration   |                   |

| 000 000                       | sll      | $RD = RS1 \ll 1$  |

| 000 010                       | srl      | RD = RS1 >> 1     |

| Arithmetic, Logical Operation |          |                   |

| 100 011                       | add      | RD = RS1 + RS2    |

| 100 010                       | sub      | RD = RS1 - RS2    |

| 100 110                       | and      | $RD=RS1\wedgeRS2$ |

| 100 101                       | or       | $RD=RS1\lorRS2$   |

| 100 100                       | xor      | $RD=RS1\oplusRS2$ |

Table: R-type Instructions (in R-type instructions  $IR[31:26] = 0^6$ )

Convert the C code segment below to a simplified DLX's machine code.

if (i==j)

goto L1;

f=g+h;

L1: f=f-i;

| Variable | Register |  |

|----------|----------|--|

| f        | R1       |  |

| g        | R2       |  |

| h        | R3       |  |

| i        | R4       |  |

| j        | R5       |  |

Table: Register assignment for Example 1

PC < PC+1 + [IMM]

Convert the C code segment below to a simplified DLX's machine code.

| array | A | in C         |

|-------|---|--------------|

| [0]A  |   | <b>K</b> A   |

| ACIJ  |   | <u></u> ↓+ A |

| •     |   | A +2         |

| (     |   |              |

| (     |   | (            |

| 1     |   |              |

| Variable | Register |        |

|----------|----------|--------|

| g        | R1       | A RCOT |

| h        | R2       | Arther |

| i        | R3       |        |

| j        | R4       | 6:10   |

| A        | R5       | ACIJE  |

| A+i      | R6       | Ati J  |

| A[i]     | R7       | R7     |

| i!=h     | R8       |        |

# Code Conversion

|                                                   | A $RS$<br>Ati $RG$<br>Ati] $RT$<br>izh $RB$                                                                                  | G RI<br>L R2<br>L R3<br>J R4            |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| C code                                            | DLX's machine cod                                                                                                            |                                         |

| LOOP: g=g+A[i];<br>i=i+j;<br>if (i!=h) goto LOOP; | add R6 R5 R3.<br>Iw R7 R6 0<br>add R1 R1 R7, c:3<br>add R3 R3 R4<br>xor R8 R3 R2<br>bnez R8 $-6$ pc<br>-6<br>PC+1+ $\sum mm$ | RG ← A + i<br>R7 ← A[;]<br>R1 ← g+ A(;] |

- In this chapter we described the ISA of the simplified DLX.

- Even though the ISA is rather simple, C instructions and programs can be translated to the DLX machine language.

- Missing in this description is supporting systems calls, distinguishing between protected mode and user mode, etc.